2.6.5.4.8. Avalon-MM Interface Signals

The Avalon-MM interface is an Avalon-MM slave port. This interface uses word

addressing and provides access to the 16-bit configuration registers of the PHY.

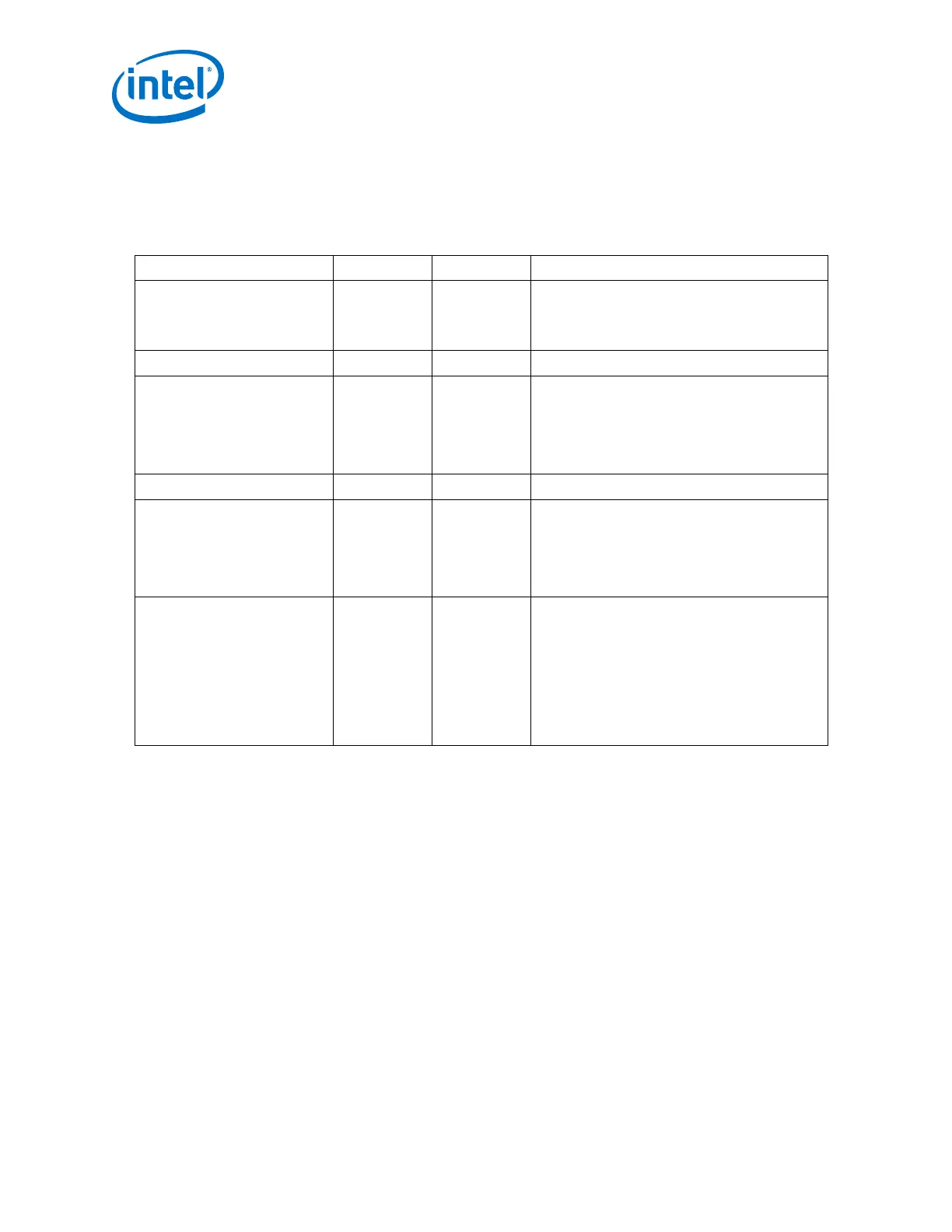

Table 165. Avalon-MM Interface Signals

Signal Name Direction Width Description

csr_address

Input 5, 11 Use this bus to specify the register address to read

from or write to. The width is:

• 5 bits for 2.5G and 1G/2.5G configurations.

• 11 bits for 1G/2.5G/5G/10G configurations.

csr_read

Input 1 Assert this signal to request a read operation.

csr_readdata

Output 16, 32 Data read from the specified register. The data is

valid only when the csr_waitrequest signal is

deasserted. The width is:

• 16 bits for 2.5G and 1G/2.5G configurations.

• 32 bits for 1G/2.5G/5G/10G configurations. The

upper 16 bits are reserved.

csr_write

Input 1 Assert this signal to request a write operation.

csr_writedata

Input 16, 32 Data to be written to the specified register. The

data is written only when the csr_waitrequest

signal is deasserted. The width is:

• 16 bits for 2.5G and 1G/2.5G configurations.

• 32 bits for 1G/2.5G/5G/10G configurations. The

upper 16 bits are reserved.

csr_waitrequest

Output 1 When asserted, indicates that the PHY is busy and

not ready to accept any read or write requests.

• When you have requested for a read or write,

keep the control signals to the Avalon-MM

interface constant while this signal is asserted.

The request is complete when it is deasserted.

• This signal can be high or low during idle cycles

and reset. Therefore, the user application must

not make any assumption of its assertion state

during these periods.

2.6.6. XAUI PHY IP Core

In a XAUI configuration, the transceiver channel data path is configured using a soft

PCS. The XAUI configuration provides the transceiver channel datapath, clocking, and

channel placement guidelines. You can implement a XAUI link using the IP Catalog.

Under Ethernet in the Interfaces menu, select the XAUI PHY IP core. The XAUI PHY IP

core implements the XAUI PCS in soft logic.

XAUI is a specific physical layer implementation of the 10 Gigabit Ethernet link defined

in the IEEE 802.3ae-2008 specification. The XAUI PHY uses the XGMII interface to

connect to the IEEE802.3 MAC and Reconciliation Sublayer (RS). The IEEE

802.3ae-2008 specification requires the XAUI PHY link to support:

• A 10 Gbps data rate at the XGMII interface

• Four lanes each at 3.125 Gbps at the PMD interface

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

214

Loading...

Loading...