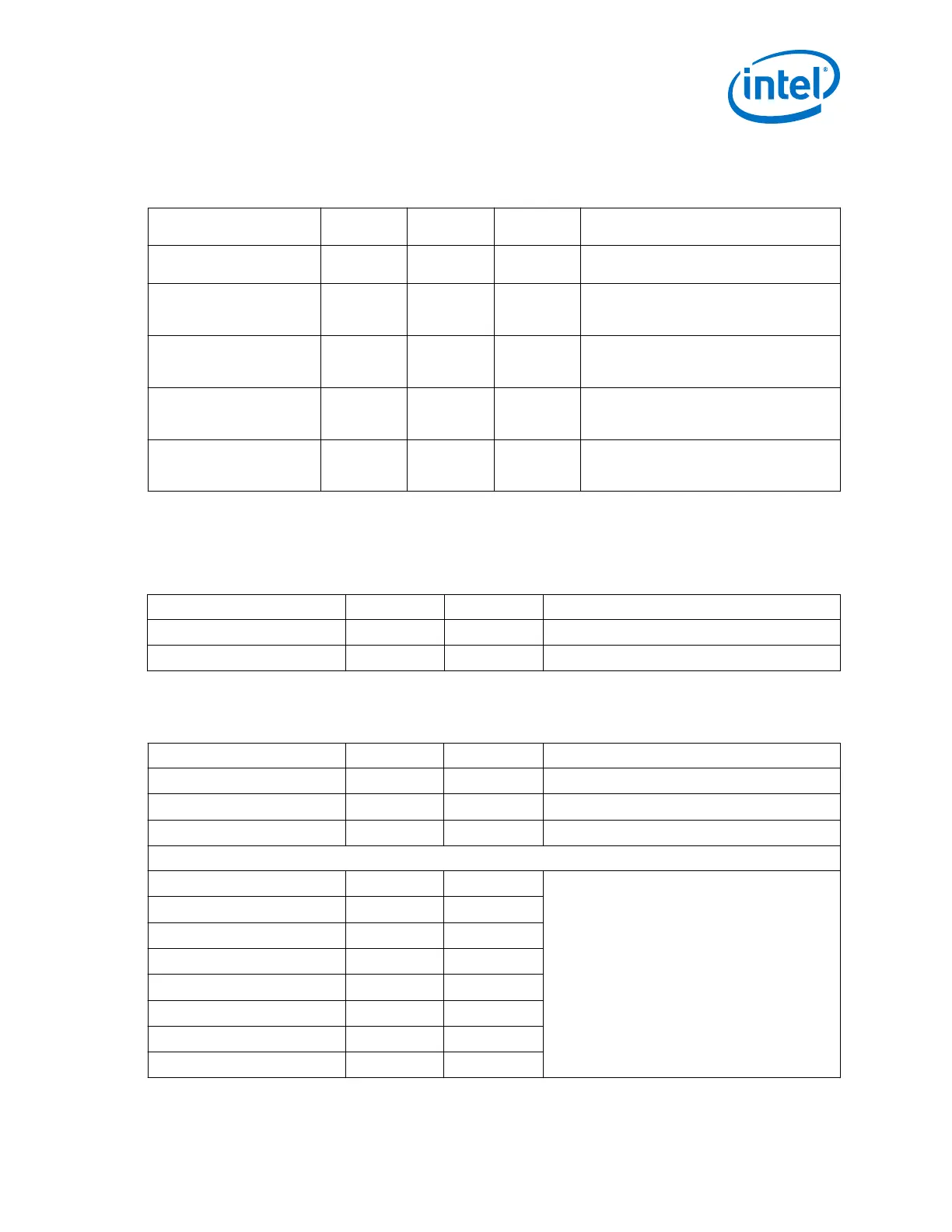

2.6.5.4.5. Status Signals

Table 162. Status Signals

Signal Name Direction Clock

Domain

Width Description

led_char_err

Output 1 Asserted when a 10-bit character error is

detected in the RX data.

led_link

Output Synchronous

to

tx_clkout

1 Asserted when the link synchronization for

1GbE or 2.5GbE is successful

led_disp_err

Output Synchronous

to

rx_clkout

1 Asserted when a 10-bit running disparity

error is detected in the RX data.

led_an

Output Synchronous

to

rx_clkout

1 Asserted when auto-negotiation is

completed.

rx_block_lock

Output Synchronous

to

rx_clkout

1 Asserted when the link synchronization for

10GbE is successful.

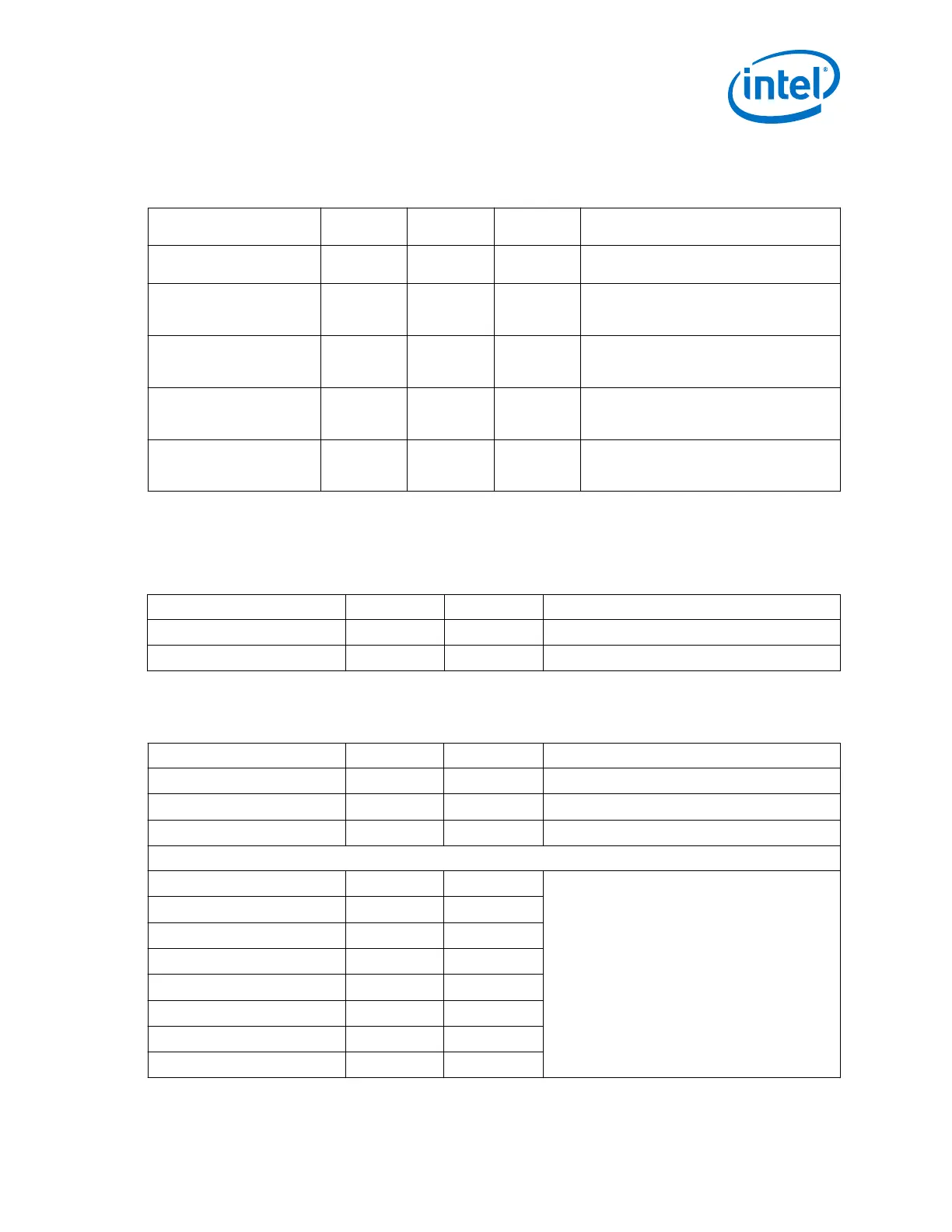

2.6.5.4.6. Serial Interface Signals

The serial interface connects to an external device.

Table 163. Serial Interface Signals

Signal Name Direction Width Description

tx_serial_data

Output 1 TX data.

rx_serial_data

Input 1 RX data.

2.6.5.4.7. Transceiver Status and Reconfiguration Signals

Table 164. Control and Status Signals

Signal Name Direction Width Description

rx_is_lockedtodata

Output 1 Asserted when the CDR is locked to the RX data.

tx_cal_busy

Output 1 Asserted when TX calibration is in progress.

rx_cal_busy

Output 1 Asserted when RX calibration is in progress.

Transceiver reconfiguration signals for Arria 10 devices

reconfig_clk

Input 1 Reconfiguration signals connected to the

reconfiguration block. The reconfig_clk signal

provides the timing reference for this interface.

reconfig_reset

Input 1

reconfig_address

Input 10

reconfig_write

Input 1

reconfig_read

Input 1

reconfig_writedata

Input 32

reconfig_readdata

Output 32

reconfig_waitrequest

Output 1

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

213

Loading...

Loading...