Signal Name Direction Width Description

• 8 bits for 1G/2.5G/10G configurations.

• 4 bits for 1G/2.5G/5G/10G configurations.

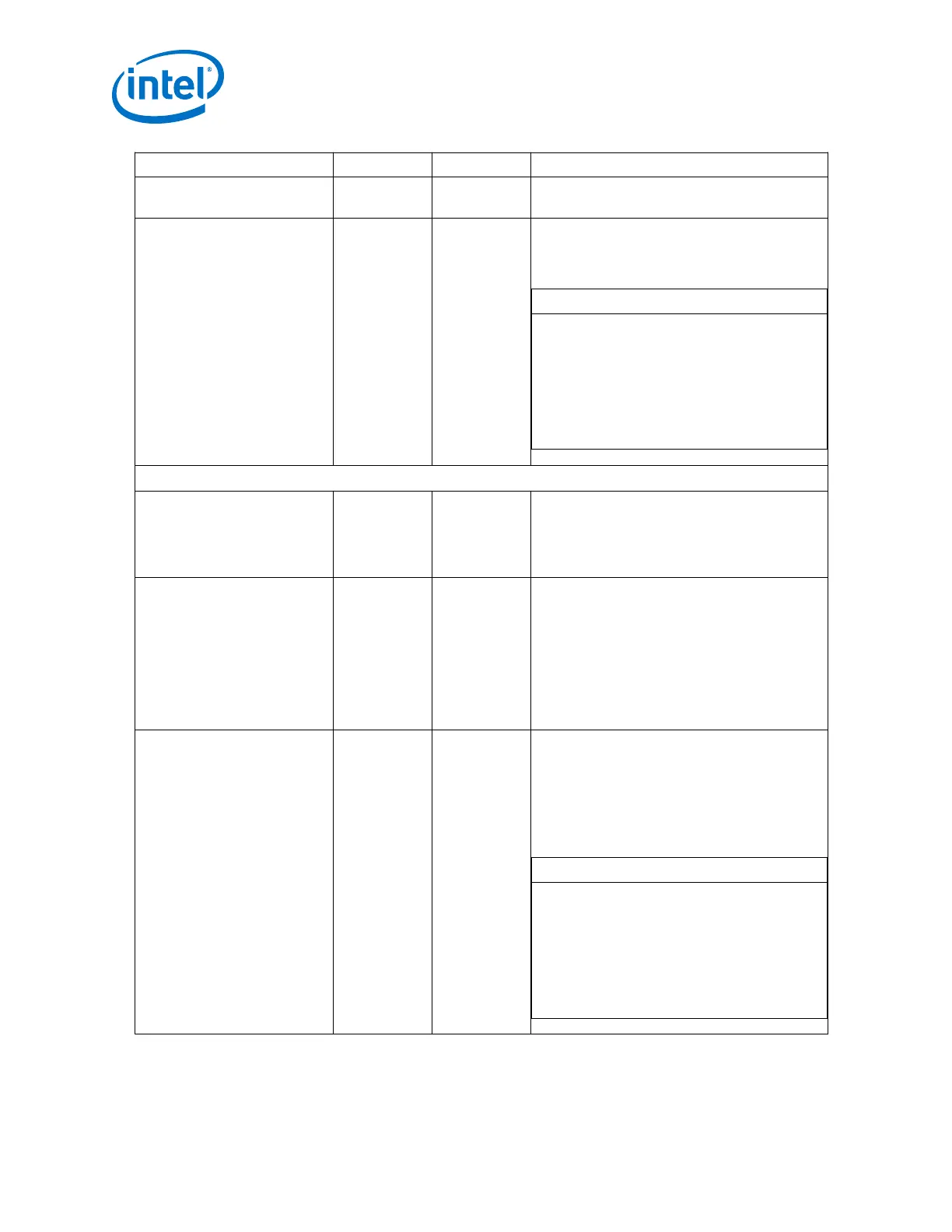

xgmii_tx_valid

Output 1

Indicates valid data on xgmii_tx_control and

xgmii_tx_data from the MAC.

Your logic/MAC must toggle the valid data as

shown below:

Speed Toggle Rate

1G Asserted once every 10

clock cycles

2.5G Asserted once every 4

clock cycles

5G Asserted once every 2

clock cycles

10G Always asserted

RX XGMII signals—synchronous to xgmii_rx_coreclkin

xgmii_rx_data

Output 64, 32 RX data to the MAC. The PHY sends the data in the

following order: bits[7:0], bits[15:8], and so forth.

The width is:

• 64 bits for 1G/2.5G/10G configurations.

• 32 bits for 1G/2.5G/5G/10G configurations.

xgmii_rx_control

Output 8, 4 RX control to the MAC.

•

xgmii_rx_control[0] corresponds to

xgmii_rx_data[7:0]

•

xgmii_rx_control[1] corresponds to

xgmii_rx_data[15:8]

• and so forth.

The width is:

• 8 bits for 1G/2.5G/10G configurations.

• 4 bits for 1G/2.5G/5G/10G configurations.

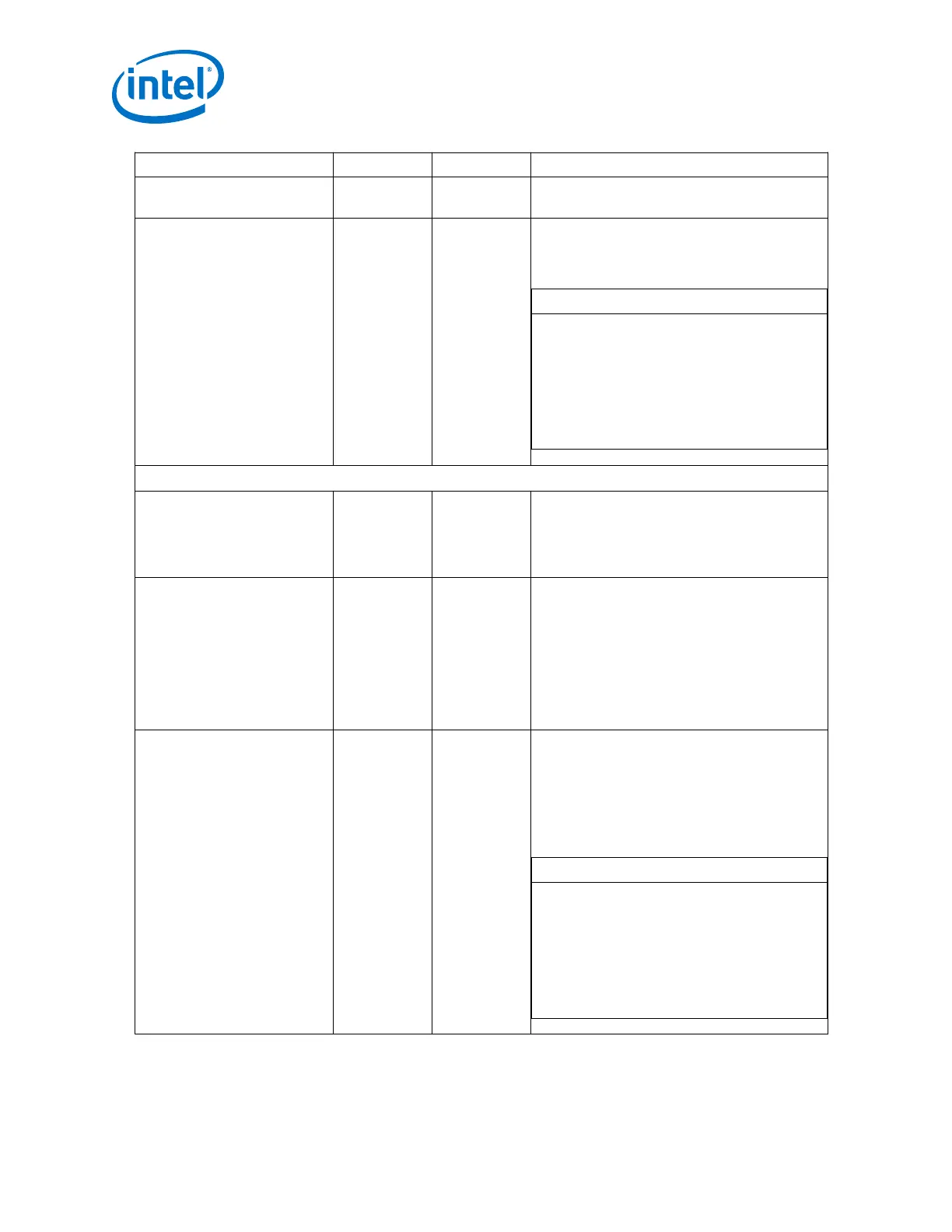

xgmii_rx_valid

Output 1

Indicates valid data on xgmii_rx_control and

xgmii_rx_data from the MAC.

The toggle rate from the PHY is shown in the table

below.

Note: The toggle rate may vary when the start of

a packet is received or when rate match

occurs inside the PHY. You should not

expect the valid data pattern to be fixed.

Speed Toggle Rate

1G Asserted once every 10

clock cycles

2.5G Asserted once every 4

clock cycles

5G Asserted once every 2

clock cycles

10G Always asserted

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

212

Loading...

Loading...