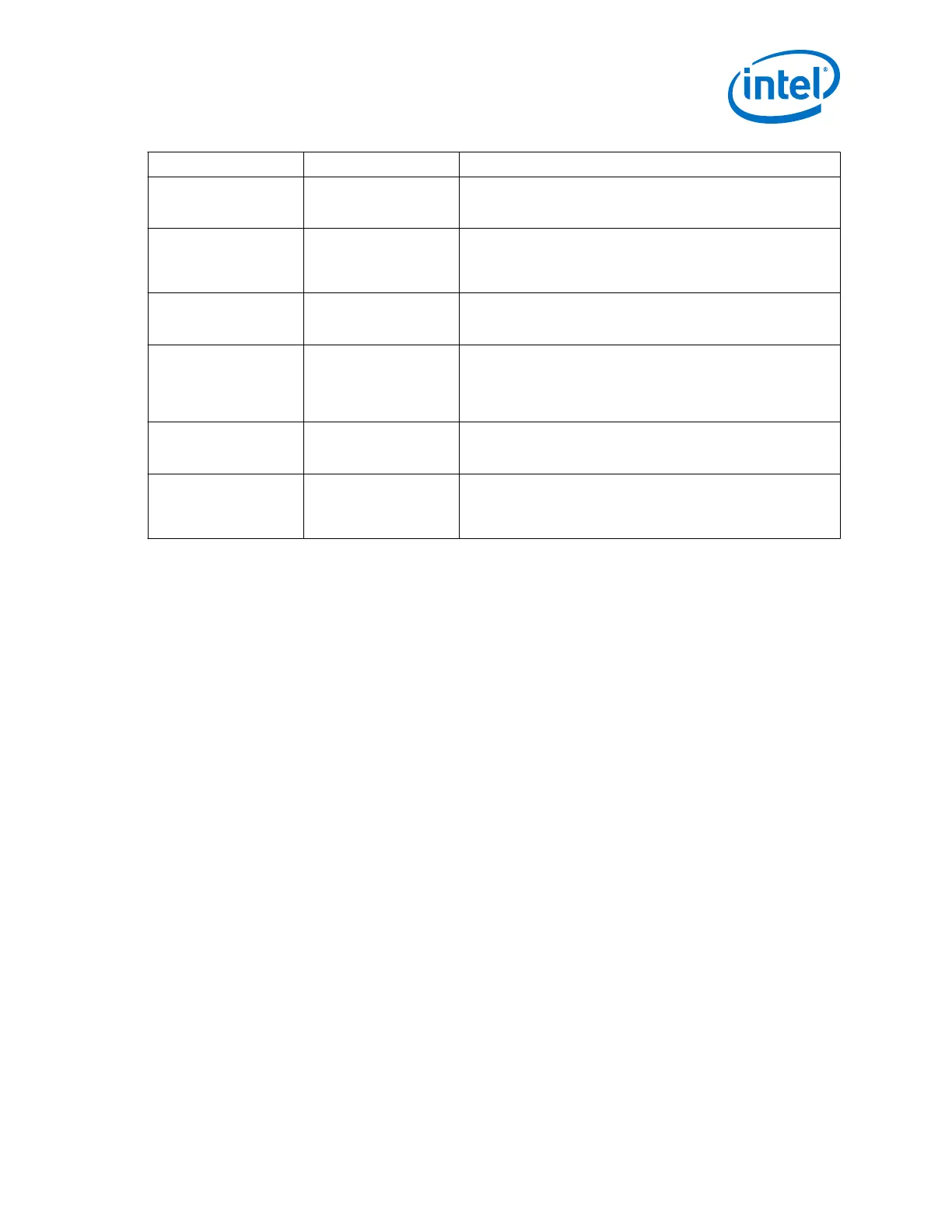

Parameters Value Description

Enable

rx_pma_qpipulldn port

(QPI)

On/Off

Enables the rx_pma_qpipulldn control input port. Use this port

only for QPI applications.

Enable

rx_is_lockedtodata

port

On/Off

Enables the optional rx_is_lockedtodata status output port.

This signal indicates that the RX CDR is currently in lock to data

mode or is attempting to lock to the incoming data stream. This is

an asynchronous output signal.

Enable

rx_is_lockedtoref port

On/Off

Enables the optional rx_is_lockedtoref status output port.

This signal indicates that the RX CDR is currently locked to the

CDR reference clock. This is an asynchronous output signal.

Enable

rx_set_lockedtodata

port and

rx_set_lockedtoref

ports

On/Off

Enables the optional rx_set_lockedtodata and

rx_set_lockedtoref control input ports. You can use these

control ports to manually control the lock mode of the RX CDR.

These are asynchronous input signals.

Enable rx_seriallpbken

port

On/Off

Enables the optional rx_seriallpbken control input port. The

assertion of this signal enables the TX to RX serial loopback path

within the transceiver. This is an asynchronous input signal.

Enable PRBS (Pseudo

Random Bit Sequence)

verifier control and

status port

On/Off

Enables the optional rx_prbs_err, rx_prbs_clr, and

rx_prbs_done control ports. These ports control and collect

status from the internal PRBS verifier.

Related Information

• PLLs and Clock Networks on page 347

• Channel Bonding on page 389

• Continuous Time Linear Equalization (CTLE) on page 452

• Decision Feedback Equalization (DFE) on page 454

• Analog Parameter Settings on page 585

• How to Enable CTLE and DFE on page 456

2.4.4. Enhanced PCS Parameters

This section defines parameters available in the Native PHY IP core GUI to customize

the individual blocks in the Enhanced PCS.

The following tables describe the available parameters. Based on the selection of the

Transceiver Configuration Rule , if the specified settings violate the protocol

standard, the Native PHY IP core Parameter Editor prints error or warning

messages.

Note: For detailed descriptions about the optional ports that you can enable or disable, refer

to the Enhanced PCS Ports section.

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

55

Loading...

Loading...