If your design has custom reset logic, replace the

*<IP_INSTANCE_NAME>*tx_digitalreset*r_reset with the source register for

the TX PCS reset signal, tx_digitalreset.

For more information about the set_max_skew constraint, refer to the SDC and

Timing Analyzer API Reference Manual.

Related Information

SDC and Timing Analyzer API Reference Manual

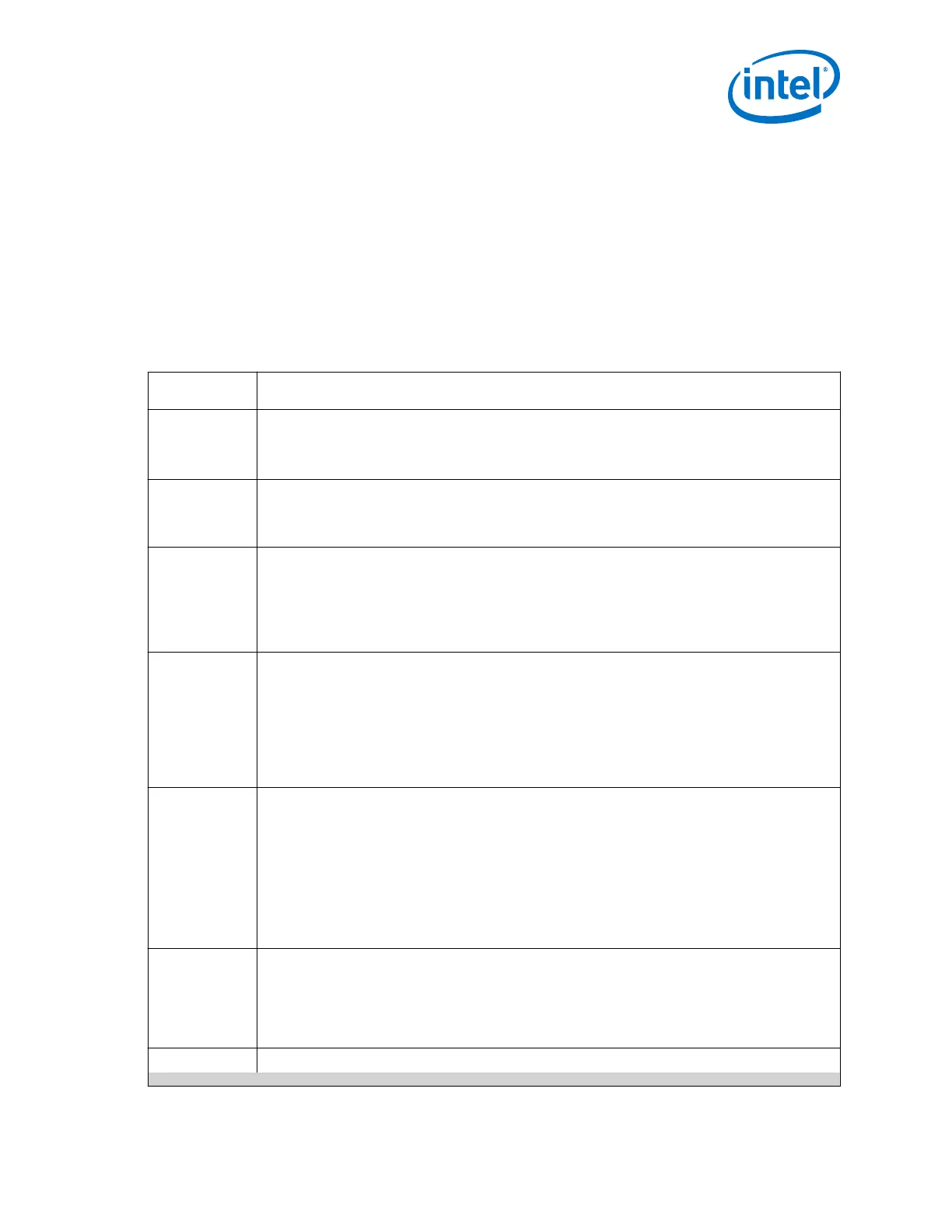

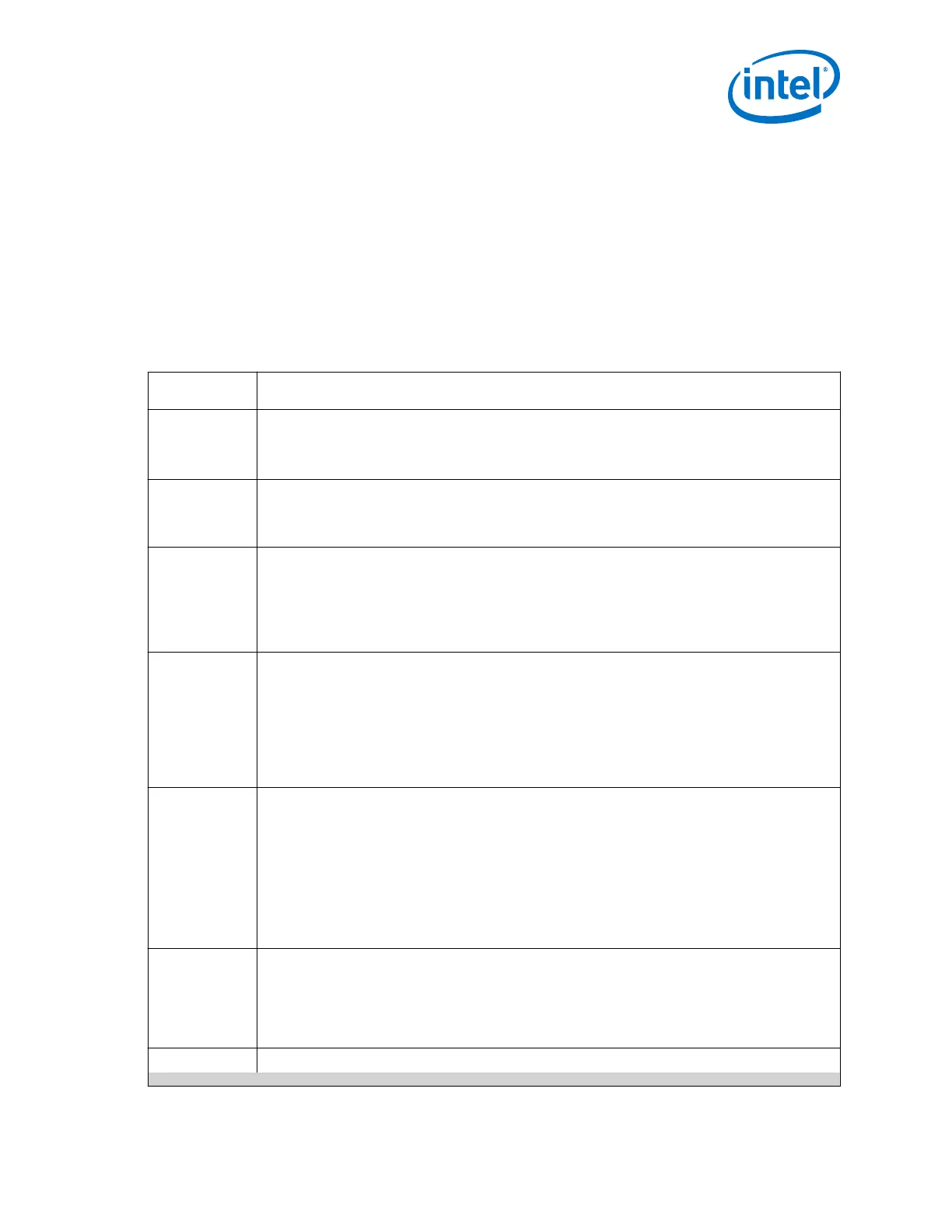

4.8. Resetting Transceiver Channels Revision History

Document

Version

Changes

2018.06.15 Made the following changes:

• Clarified the Dynamic Reconfiguration of Receiver Channel Using the Acknowledgment Model

instructions for when the CDR is in manual lock mode.

• Updated the description for the "Enable RX channel reset control" parameter.

2017.11.06 Made the following change:

• Added a note "If the design is not able to meet the maximum skew tolerance requirement with a

positive margin, Intel recommends reassigning the channels locations that are not adjacent to the

PCIe Hard IP block."

2016.05.02 Made the following changes

• Added port "user reset" in "Typical Transceiver PHY Implementation" diagram.

• Added note number 50.

• Updated "Transceiver and Receiver Reset Sequence" diagram.

• Added a note "Area in gray is don't care zone" in every diagram that has gray area in it.

• Changes "tLTD" to "trx_digitalreset" in all the diagrams.

2015.12.18 Made the following changes:

• Added description to the "Recommended Reset Sequence" section.

• Added the "Arria 10 Default Settings Preset" figure.

• Changed the signals and added a note in the "Typical Transceiver PHY Implementation" figure.

• Added a parameter to the "General Options" table.

• Updated the "Reset Sequence Timing Diagram for Receiver when CDR is in Manual Lock Mode"

figure.

• Updated the steps in the "Resetting the Transceiver in CDR Manual Lock Mode" section.

2015.11.02 Made the following changes:

• Updated the "Reset Conditions" table.

• Created the "Transceiver PHY Implementation" section.

• Updated the "Typical Transceiver PHY Implementation" figure and moved it to the "Transceiver PHY

Implementation" section.

• Added the "Model 1: Default Model" and "Model 2: Acknowledgment Model" sections to the "How Do

I Reset?" section.

• Updated the "Altera Transceiver PHY Reset Controller System Diagram" in the "Using the Altera

Transceiver PHY Reset Controller" section.

• Added "Usage Examples for pll_select" to the "Transceiver PHY Reset Controller Interfaces" section.

2014.12.15 Made the following changes:

• Updated the "Transmitter Reset Sequence After Power-Up" and "Transmitter Reset Sequence During

Device Operation" figures.

• Improved formatting in the "Transceiver PHY Reset Controller IP Core Top-Level Signals" figure.

• Updated the description of the reset, tx_analogreset, and rx_analogreset parameters in the

"Top-Level Signals" table.

2014.08.15 Made the following changes:

continued...

4. Resetting Transceiver Channels

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

445

Loading...

Loading...