2.4.8. PMA Ports

This section describes the PMA and calibration ports for the Arria 10 Transceiver Native

PHY IP core.

The following tables, the variables represent these parameters:

• <n>—The number of lanes

• <d>—The serialization factor

• <s>—The symbol size

• <p>—The number of PLLs

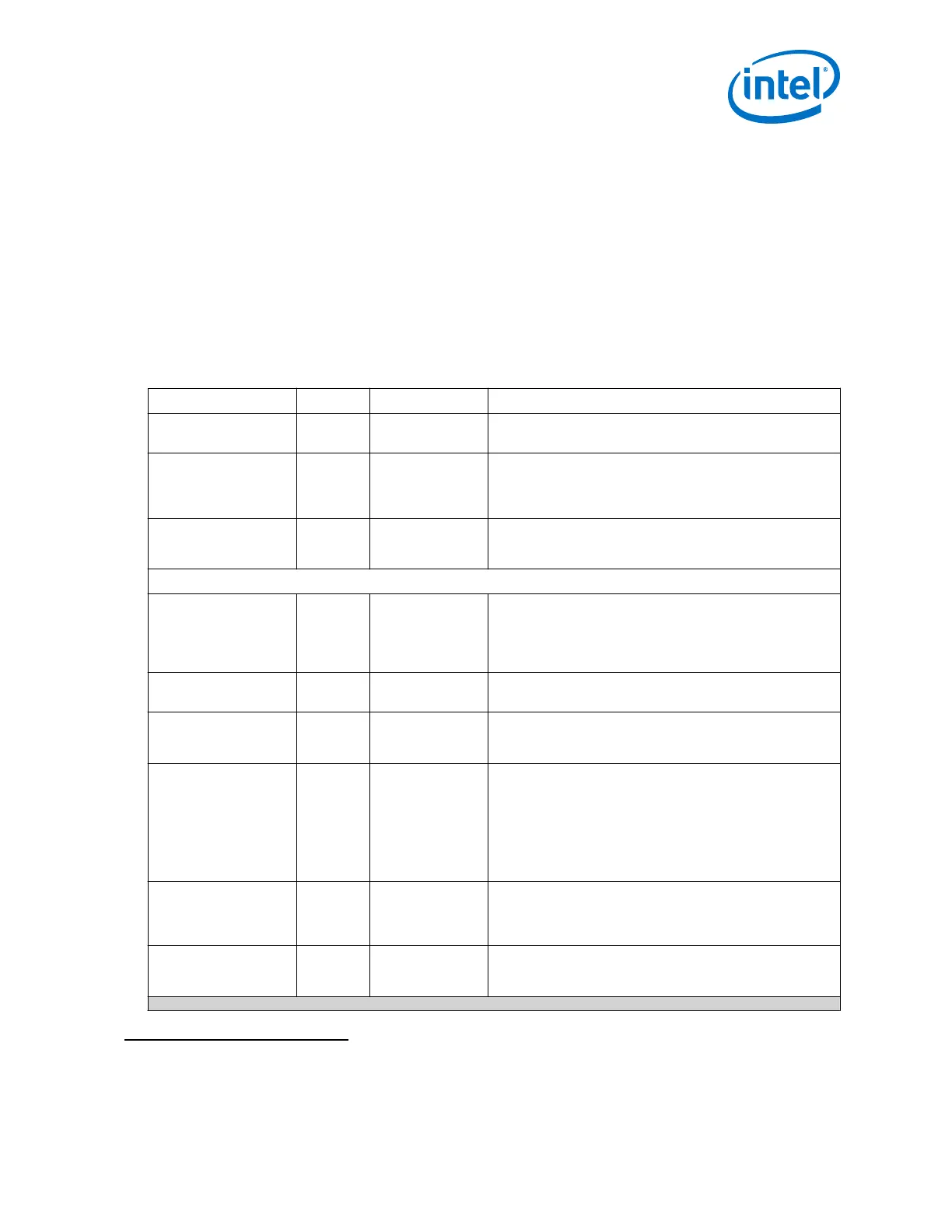

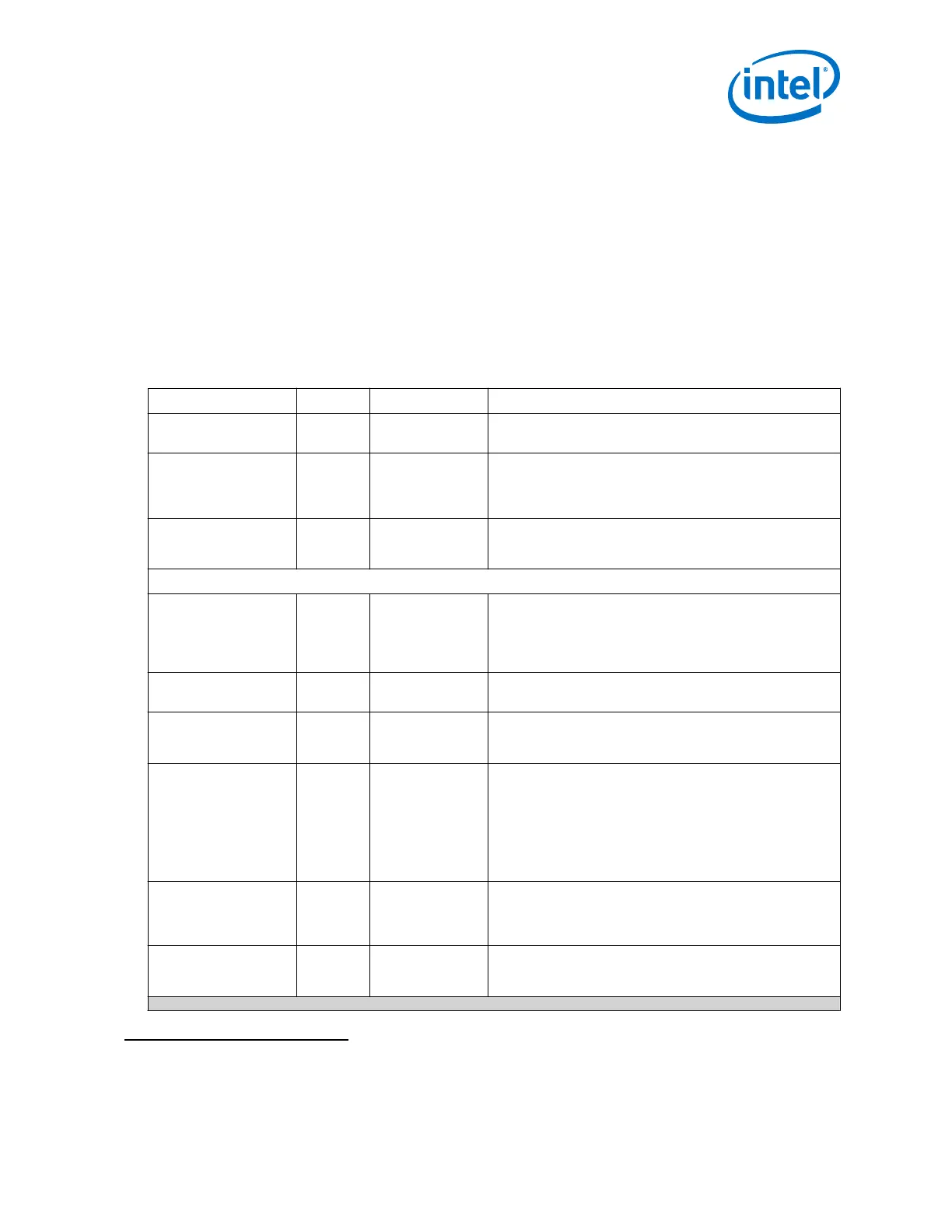

Table 45. TX PMA Ports

Name Direction Clock Domain Description

tx_serial_data[<n>

-1:0]

Input N/A This is the serial data output of the TX PMA.

tx_serial_clk0

Input Clock This is the serial clock from the TX PLL. The frequency of this

clock depends on the data rate and clock division factor. This

clock is for non bonded channels only. For bonded channels

use the tx_bonding_clocks clock TX input.

tx_bonding_clocks[

<n><6>-1:0]

Input Clock This is a 6-bit bus which carries the low speed parallel clock

per channel. These clocks are outputs from the master CGB.

Use these clocks for bonded channels only.

Optional Ports

tx_serial_clk1

tx_serial_clk2

tx_serial_clk3

tx_serial_clk4

Inputs Clocks These are the serial clocks from the TX PLL. The frequency of

these clocks depends on the data rate and clock division

factor. These additional ports are enabled when you specify

more than one TX PLL.

tx_analog_reset_ac

k

Output Asynchronous

Enables the optional tx_pma_analog_reset_ack output.

This port should not be used for register mode data transfers

tx_pma_clkout

Output Clock This clock is the low speed parallel clock from the TX PMA. It

is available when you turn on Enable tx_pma_clkout port

in the Transceiver Native PHY IP core Parameter Editor.

(33)

tx_pma_div_clkout

Output Clock

If you specify a tx_pma_div_clkout division factor of 1 or

2, this clock output is derived from the PMA parallel clock

(low speed parallel clock). If you specify a

tx_pma_div_clkout division factor of 33, 40, or 66, this

clock is derived from the PMA serial clock. This clock is

commonly used when the interface to the TX FIFO runs at a

different rate than the PMA parallel clock frequency, such as

66:40 applications.

tx_pma_iqtxrx_clko

ut

Output Clock This port is available if you turn on Enable tx_

pma_iqtxrx_clkout port in the Transceiver Native PHY IP

core Parameter Editor. This output clock can be used to

cascade the TX PMA output clock to the input of a PLL.

tx_pma_elecidle[<n

>-1:0]

Input Asynchronous When you assert this signal, the transmitter is forced to

electrical idle. This port has no effect when you configure the

transceiver for the PCI Express protocol.

continued...

(33)

This clock is not to be used to clock the FPGA - transceiver interface. This clock may be used

as a reference clock to an external clock cleaner.

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

73

Loading...

Loading...