1. Arria

®

10 Transceiver PHY Overview

This user guide provides details about the Arria

®

10 transceiver physical (PHY) layer

architecture, PLLs, clock networks, and transceiver PHY IP. It also provides protocol

specific implementation details and describes features such as transceiver reset and

dynamic reconfiguration of transceiver channels and PLLs.

Intel

®

Arria 10 FPGAs offer up to 96 GX transceiver channels with integrated advanced

high speed analog signal conditioning and clock data recovery techniques for chip-to-

chip, chip-to-module, and backplane applications.

The Arria 10 GX and SX devices have GX transceiver channels that can support data

rates up to 17.4 Gbps for chip-to-chip applications and 12.5 Gbps for backplane

applications.

The Arria 10 GT device has up to 6 GT transceiver channels, that can support data

rates up to 25.8 Gbps for short reach chip-to-chip and chip-to-module applications.

Additionally, the GT devices have GX transceiver channels that can support data rates

up to 17.4 Gbps for chip-to-chip and 12.5 Gbps for backplane applications. If all 6 GT

channels are used in GT mode, then the GT device also has up to 54 GX transceiver

channels.

The Arria 10 transceivers support reduced power modes with data rates up to 11.3

Gbps (chip-to-chip) for critical power sensitive designs. In GX devices that have

transceivers on both sides of the device, each side can be operated independently in

standard and reduced power modes. You can achieve transmit and receive data rates

below 1.0 Gbps with oversampling.

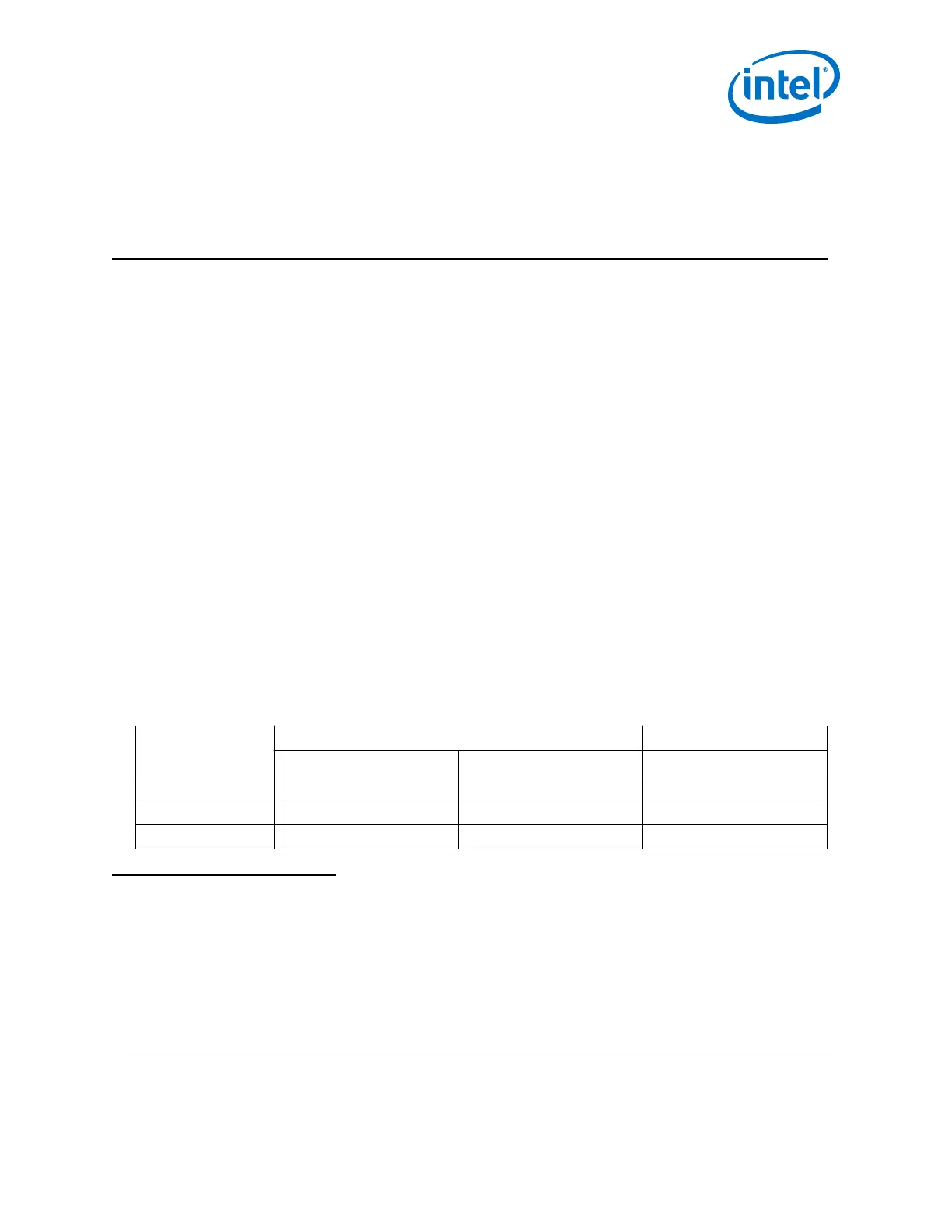

Table 1. Data Rates Supported by GX Transceiver Channel Type

Device Variant Standard Power Mode

(1),

(2)

Reduced Power Mode

(1),

(2)

Chip-to-Chip Backplane Chip-to-Chip

SX

(3)

1.0 Gbps to 17.4 Gbps 1.0 Gbps to 12.5 Gbps 1.0 Gbps to 11.3 Gbps

GX

(3)

1.0 Gbps to 17.4 Gbps 1.0 Gbps to 12.5 Gbps 1.0 Gbps to 11.3 Gbps

GT

(4)

1.0 Gbps to 17.4 Gbps 1.0 Gbps to 12.5 Gbps 1.0 Gbps to 11.3 Gbps

(1)

To operate GX transceiver channels at designated data rates in standard and reduced power

modes, apply the corresponding core and periphery power supplies. Refer to the Arria 10

Device Datasheet for more details.

(2)

The minimum operational data rate is 1.0 Gbps for both the transmitter and receiver. For

transmitter data rates less than 1.0 Gbps, oversampling must be applied at the transmitter. For

receiver data rates less than 1.0 Gbps, oversampling must be applied at the receiver.

(3)

For SX and GX device variants, the maximum transceiver data rates are specified for the

fastest (–1) transceiver speed grade.

UG-01143 | 2018.06.15

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus

and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other

countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2008

Registered

Loading...

Loading...