6.12.1. Changing VOD, Pre-emphasis Using Direct Reconfiguration Flow

1. Perform the necessary steps from steps 1 to 7 in Steps to Perform Dynamic

Reconfiguration.

2. Read from the PMA analog feature address of the channel you want to change. For

example, to change pre-emphasis 1st post-tap, read and store the value of

address 0x105.

3. Select a valid value for the feature according to the Arria 10 register map. For

example, a valid setting for pre-emphasis 1st post-tap has a bit encoding of

5'b00001.

4. Perform a read-modify-write to the address of the PMA analog feature using the

valid value. For example, to change the pre-emphasis 1st post-tap, write 5'b00001

to address 0x105.

5. Perform the necessary steps from steps 9 to 12 in Steps to Perform Dynamic

Reconfiguration.

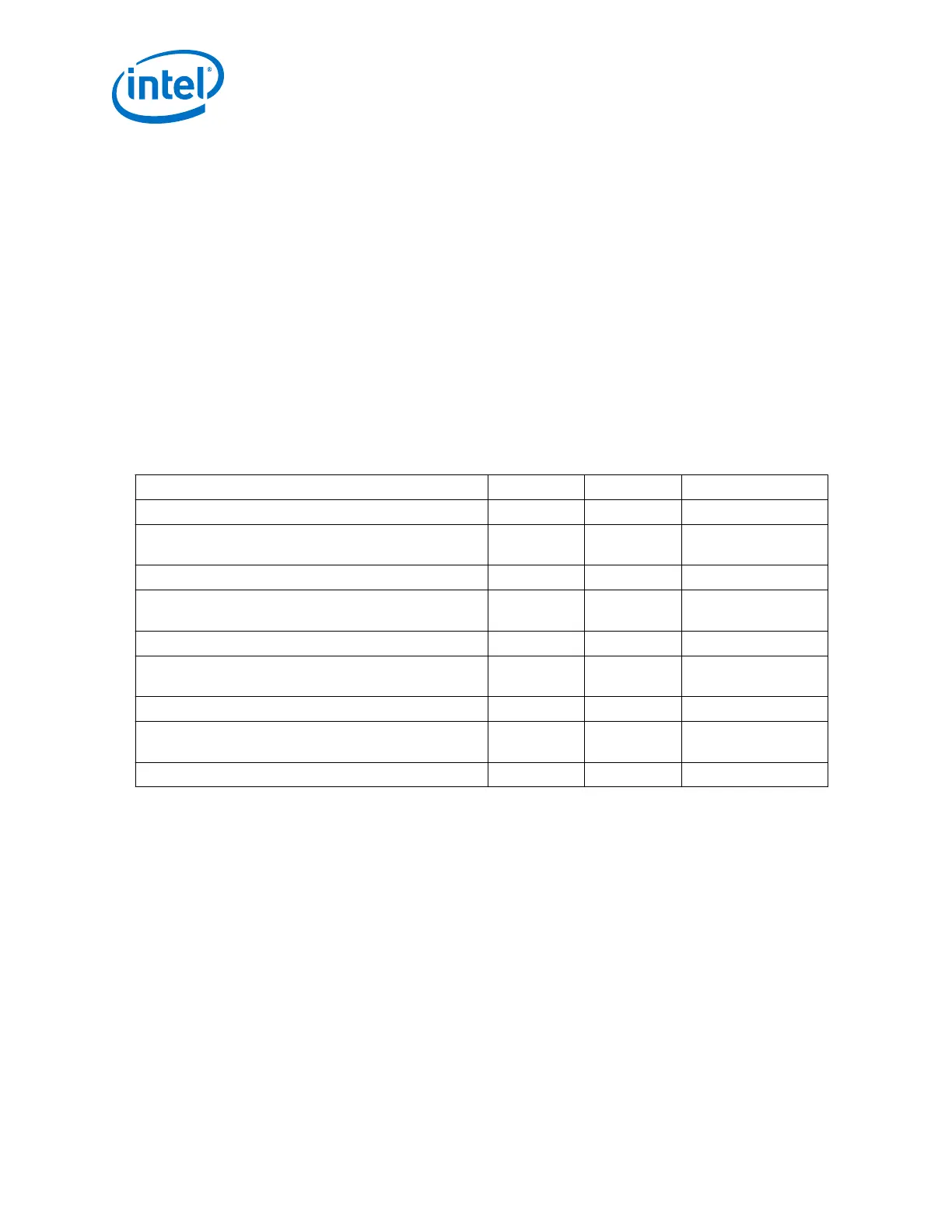

Table 274. Register Map for PMA Analog Feature

PMA Analog Feature Address Bit Values

Pre-emphasis 1st post-tap 0x105 [4:0] 5'b00000 - 5'b11001

Pre-emphasis 1st post-tap polarity 0x105 [6] 1'b0 = positive

1'b1 = negative

Pre-emphasis 2nd post-tap 0x106 [3:0] 4'b0000 - 4'b1100

Pre-emphasis 2nd post-tap polarity 0x106 [5] 1'b0 = positive

1'b1 = negative

Pre-emphasis 1st pre-tap 0x107 [4:0] 5'b00000 - 5'b10000

Pre-emphasis 1st pre-tap polarity 0x107 [5] 1'b0 = positive

1'b1 = negative

Pre-emphasis 2nd pre-tap 0x108 [2:0] 3'b000 - 3'b111

Pre-emphasis 2nd pre-tap polarity 0x108 [4] 1'b0 = positive

1'b1 = negative

Differential output voltage (V

OD

) 0x109 [4:0] 5'b00000 - 5'b11111

The PMA analog settings are governed by a set of rules. Not all combinations of V

OD

and pre-emphasis are valid. Please refer to Arria 10 Pre-Emphasis and Output Swing

Settings for current valid settings. Also, refer to "Analog Parameter Settings" and

setup guidelines on post_tap polarity settings.

Related Information

• Steps to Perform Dynamic Reconfiguration on page 516

• Arria 10 PMA Architecture on page 447

• Arria 10 Pre-Emphasis and Output Swing Settings

6. Reconfiguration Interface and Dynamic Reconfiguration

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

530

Loading...

Loading...