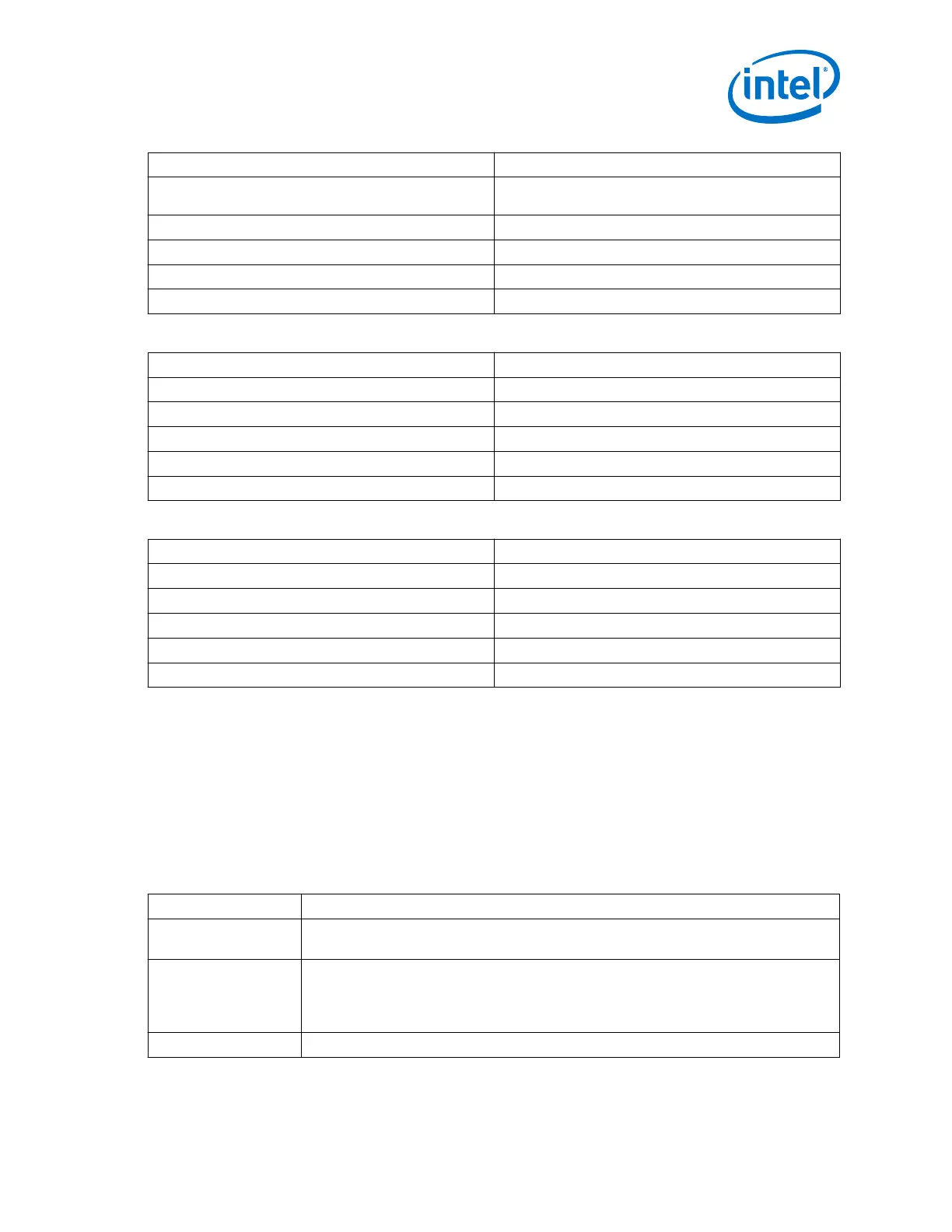

Parameter Value

Separate reconfig_waitrequest from the status of

AVMM arbitration with PreSICE

On / Off

Enable capability registers On / Off

Set user-defined IP identifier: 0 to 255

Enable control and status registers On / Off

Enable prbs soft accumulators On / Off

Table 88. Configuration Files Parameters

Parameter Value

Configuration file prefix —

Generate SystemVerilog package file On / Off

Generate C header file On / Off

Generate MIF (Memory Initialization File) On / Off

Include PMA analog settings in configuration files On / Off

Table 89. Configuration Profiles Parameters

Parameter Value

Enable multiple reconfiguration profiles On / Off

Enable embedded reconfiguration streamer On / Off

Generate reduced reconfiguration files On / Off

Number of reconfiguration profiles 1 to 8

Selected reconfiguration profile 1 to 7

Related Information

Using the Arria 10 Transceiver Native PHY IP Core on page 45

2.6. Ethernet

The Ethernet standard comprises many different PHY standards with variations in

signal transmission medium and data rates. The 1G/10GbE and 10GBASE-KR PHY IP

Core enables Ethernet connectivity at 1 Gbps and 10 Gbps over backplanes. The

10GBASE-KR PHY IP is also known as the Backplane Ethernet PHY IP. It includes link

training and auto negotiation to support the IEEE Backplane Ethernet standard.

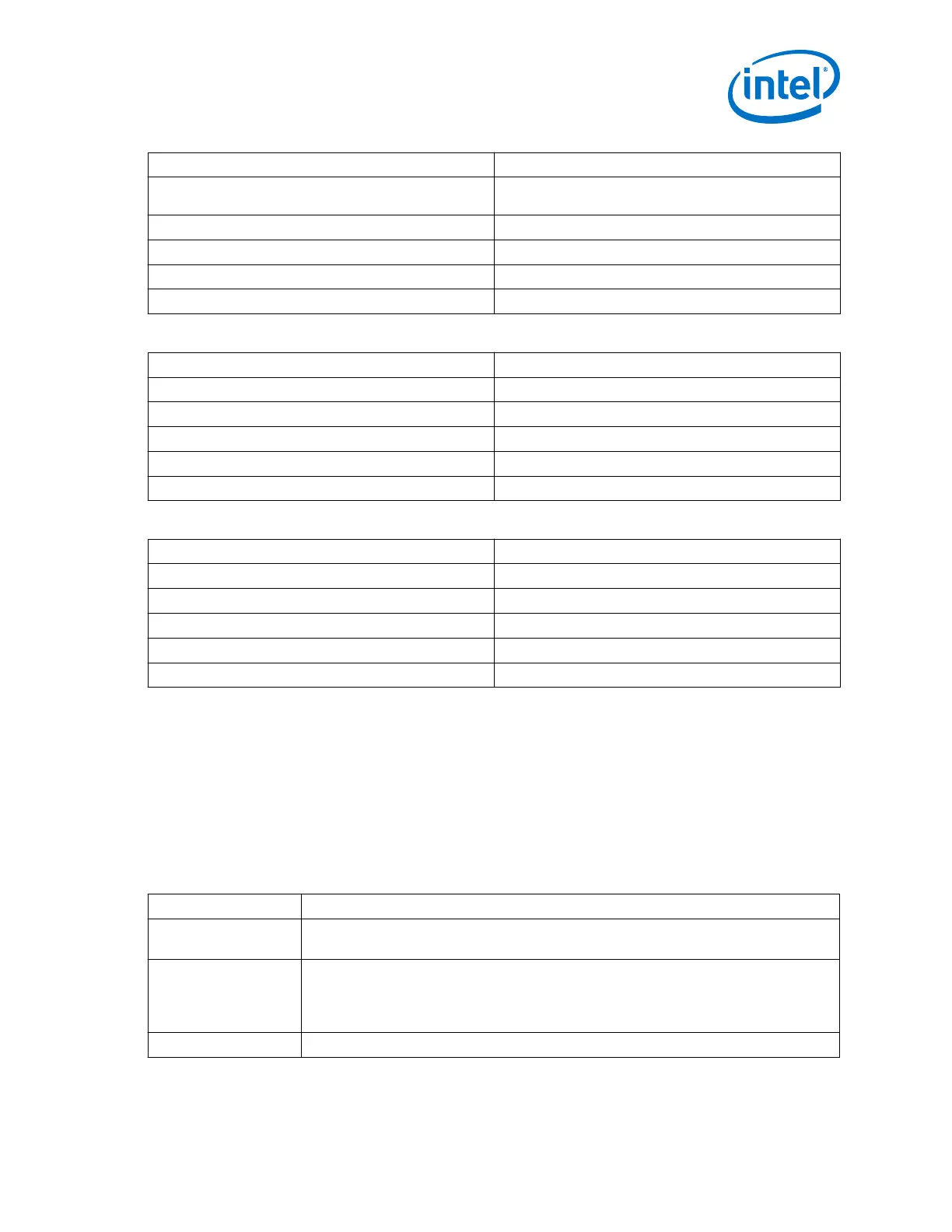

Data Rate

Transceiver Configuration Rule/IP

1G • Gigabit Ethernet

• Gigabit Ethernet 1588

10G • 10GBASE-R

• 10GBASE-R 1588

• 10GBASE-R with KR FEC

• 10GBASE-KR PHY IP

1G/10G 1G/10G Ethernet PHY IP

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

111

Loading...

Loading...