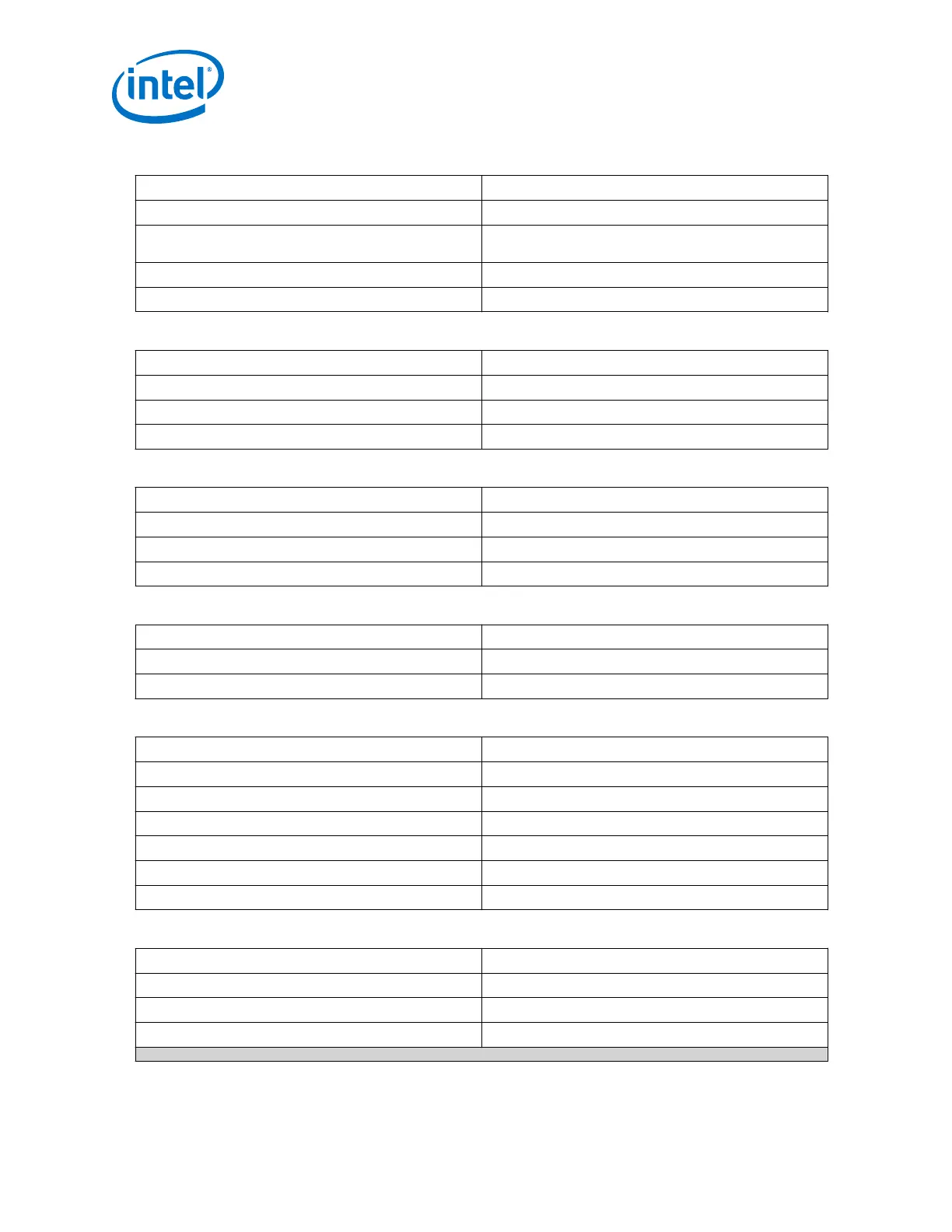

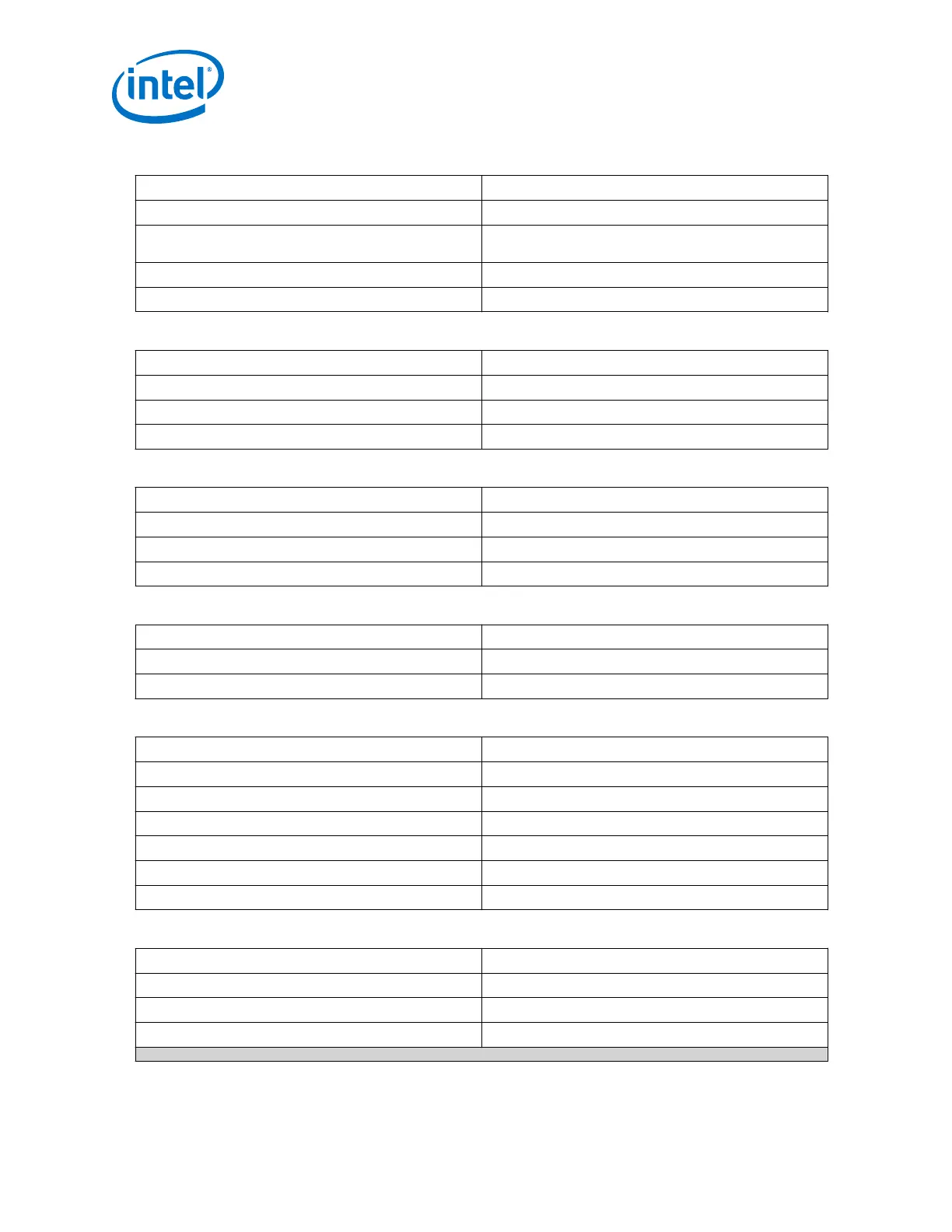

Table 82. Interlaken CRC-32 Generator and Checker Parameters

Parameter Value

Enable Interlaken TX CRC-32 generator On

Enable Interlaken TX CRC-32 generator error

insertion

On / Off

Enable Interlaken RX CRC-32 checker On

Enable rx_enh_crc32_err port On / Off

Table 83. Scrambler and Descrambler Parameters

Parameter Value

Enable TX scrambler (10GBASE-R / Interlaken) On

TX scrambler seed (10GBASE-R / Interlaken) 0x1 to 0x3FFFFFFFFFFFFFF

Enable RX descrambler (10GBASE-R / Interlaken) On

Table 84. Interlaken Disparity Generator and Checker Parameters

Parameter Value

Enable Interlaken TX disparity generator On

Enable Interlaken RX disparity checker On

Enable Interlaken TX random disparity bit On / Off

Table 85. Block Sync Parameters

Parameter Value

Enable RX block synchronizer On

Enable rx_enh_blk_lock port On / Off

Table 86. Gearbox Parameters

Parameter Value

Enable TX data bitslip Off

Enable TX data polarity inversion On / Off

Enable RX data bitslip Off

Enable RX data polarity inversion On / Off

Enable tx_enh_bitslip port Off

Enable rx_bitslip port Off

Table 87. Dynamic Reconfiguration Parameters

Parameter Value

Enable dynamic reconfiguration On / Off

Share reconfiguration interface On / Off

Enable Altera Debug Master Endpoint On / Off

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

110

Loading...

Loading...