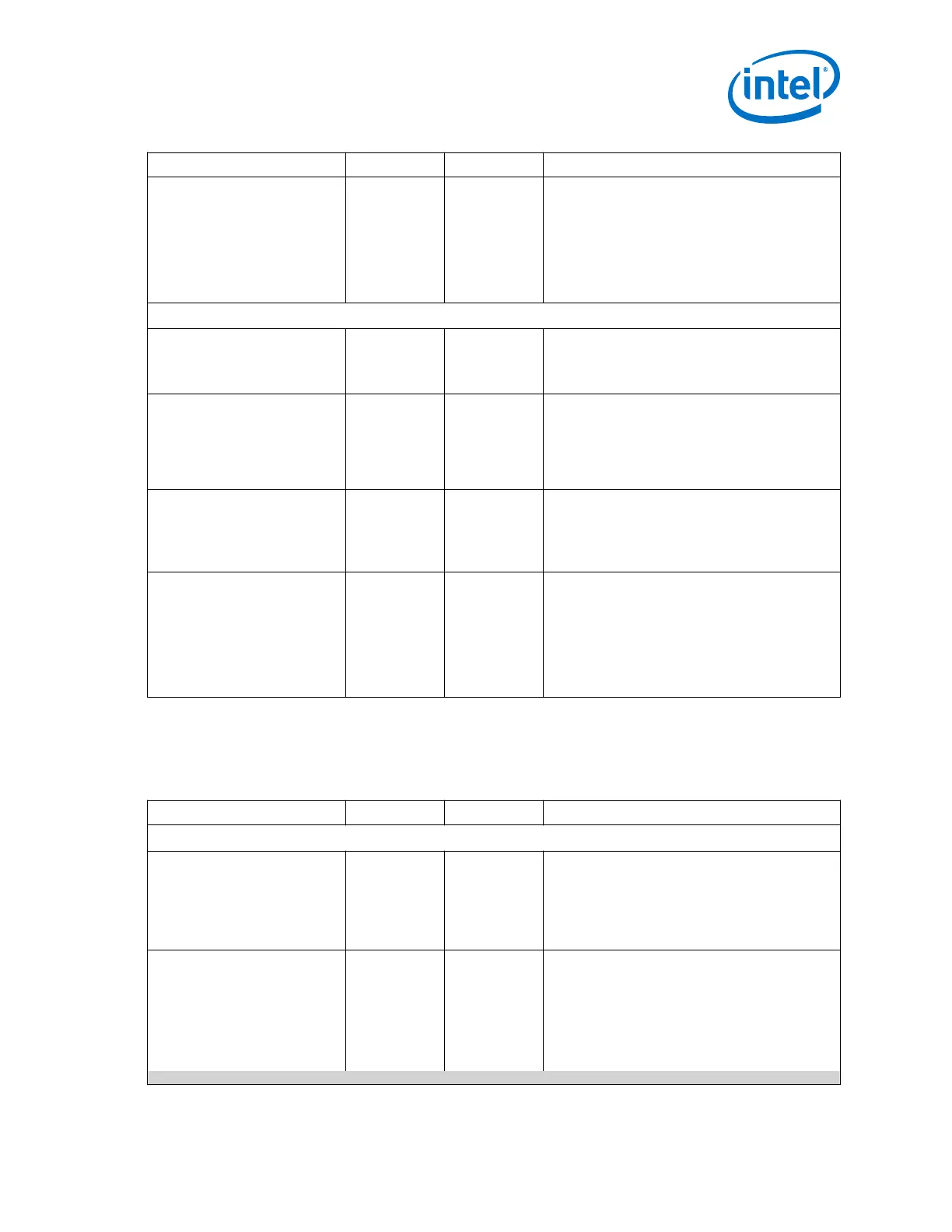

Signal Name Direction Width Description

gmii16b_tx_latency

Output 22 The latency of the PHY excluding the PMA block on

the TX datapath:

• Bits [21:10]: The number of clock cycles.

• Bits [9:0]: The fractional number of clock

cycles.

This signal is available when only the Enable IEEE

1588 Precision Time Protocol parameter is

selected.

RX GMII signals—synchronous to rx_clkout

gmii16b_rx_d

Output 16 RX data to the MAC. The PHY sends the lower byte

first followed by the upper byte. Rate matching is

done by the PHY on the RX data from the RX

recovered clock to rx_clkout.

gmii16b_rx_err

Output 2 When asserted, indicates an error. Bit[0]

corresponds to gmii16b_rx_err[7:0]; bit[1]

corresponds to gmii16b_rx_err[15:8].

The bits can be asserted at any time during a

frame transfer to indicate an error in the current

frame.

gmii16b_rx_dv

Output 2 When asserted, indicates the start of a new frame.

Bit[0] corresponds to gmii16b_rx_d[7:0]; bit[1]

corresponds to gmii16b_rx_d[15:8].

This signal remains asserted until the PHY sends

the last byte of the data frame.

gmii16b_rx_latency

Output 22 The latency of the PHY excluding the PMA block on

the RX datapath:

• Bits [21:10]: The number of clock cycles.

• Bits [9:0]: The fractional number of clock

cycles.

This signal is available only when the Enable IEEE

1588 Precision Time Protocol parameter is

selected.

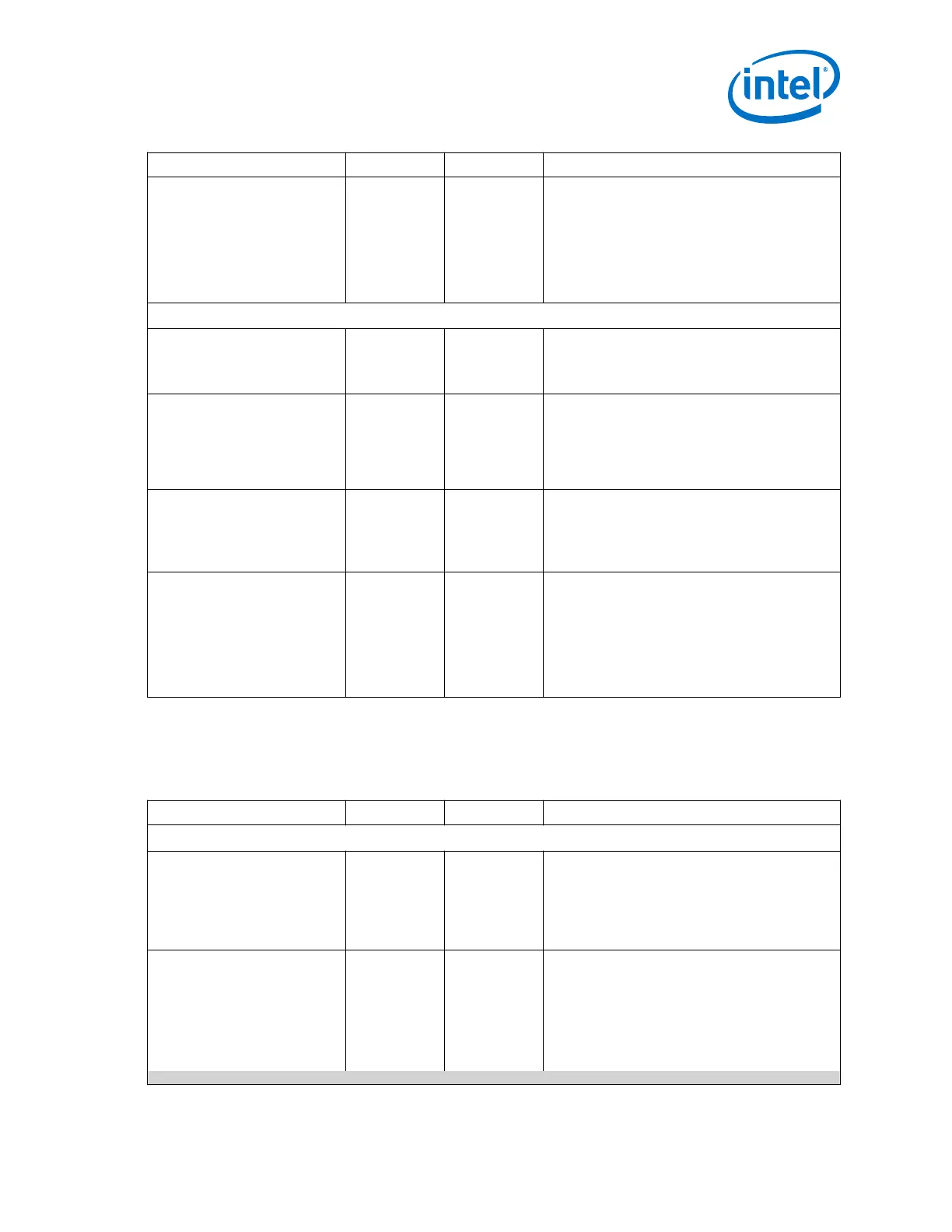

2.6.5.4.4. XGMII Signals

The XGMII supports 10GbE at 156.25 MHz.

Table 161. XGMII Signals

Signal Name Direction Width Description

TX XGMII signals—synchronous to xgmii_tx_coreclkin

xgmii_tx_data

Input 64, 32 TX data from the MAC. The MAC sends the data in

the following order: bits[7:0], bits[15:8], and so

forth.

The width is:

• 64 bits for 1G/2.5G/10G configurations.

• 32 bits for 1G/2.5G/5G/10G configurations.

xgmii_tx_control

Input 8, 4 TX control from the MAC:

•

xgmii_tx_control[0] corresponds to

xgmii_tx_data[7:0]

•

xgmii_tx_control[1] corresponds to

xgmii_tx_data[15:8]

• and so forth.

The width is:

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

211

Loading...

Loading...