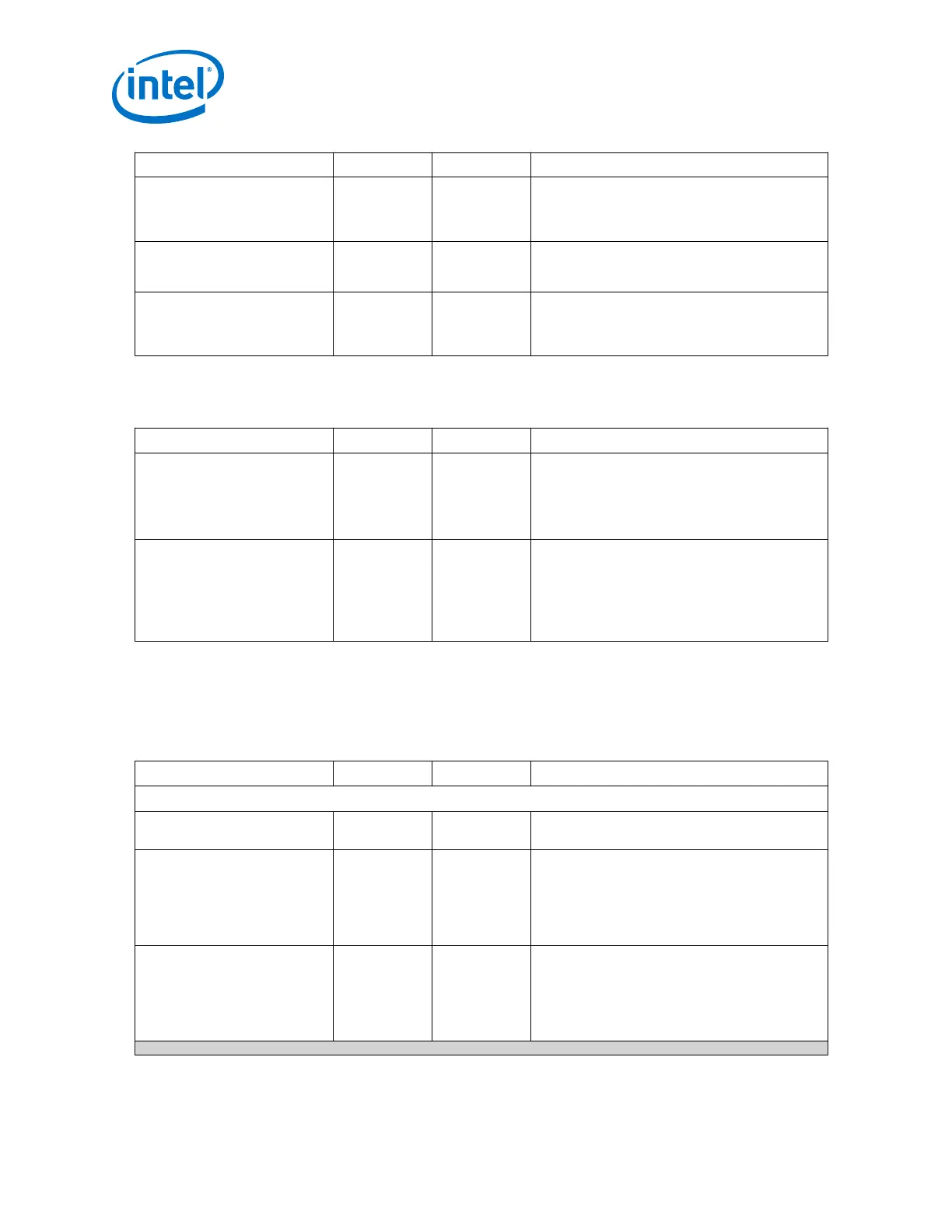

Signal Name Direction Width Description

tx_digitalreset

Input 1 Connect this signal to the Transceiver PHY Reset

Controller IP core. When asserted, triggers an

asynchronous reset to the digital logic on the TX

path.

rx_analogreset

Input 1 Connect this signal to the Transceiver PHY Reset

Controller IP core. When asserted, triggers an

asynchronous reset to the receiver CDR.

rx_digitalreset

Input 1 Connect this signal to the Transceiver PHY Reset

Controller IP core. When asserted, triggers an

asynchronous reset to the digital logic on the RX

path.

2.6.5.4.2. Operating Mode and Speed Signals

Table 159. Transceiver Mode and Operating Speed Signals

Signal Name Direction Width Description

xcvr_mode

Input 2 Connect this signal to the reconfiguration block.

Use the values below to set the speed:

• 0x0 = 1G

• 0x1 = 2.5G

• 0x3 = 10G

operating_speed

Output 3 Connect this signal to the MAC. This signal

provides the current operating speed of the PHY:

• 0x0 = 10G

• 0x1 = 1G

• 0x4 = 2.5G

• 0x5 = 5G

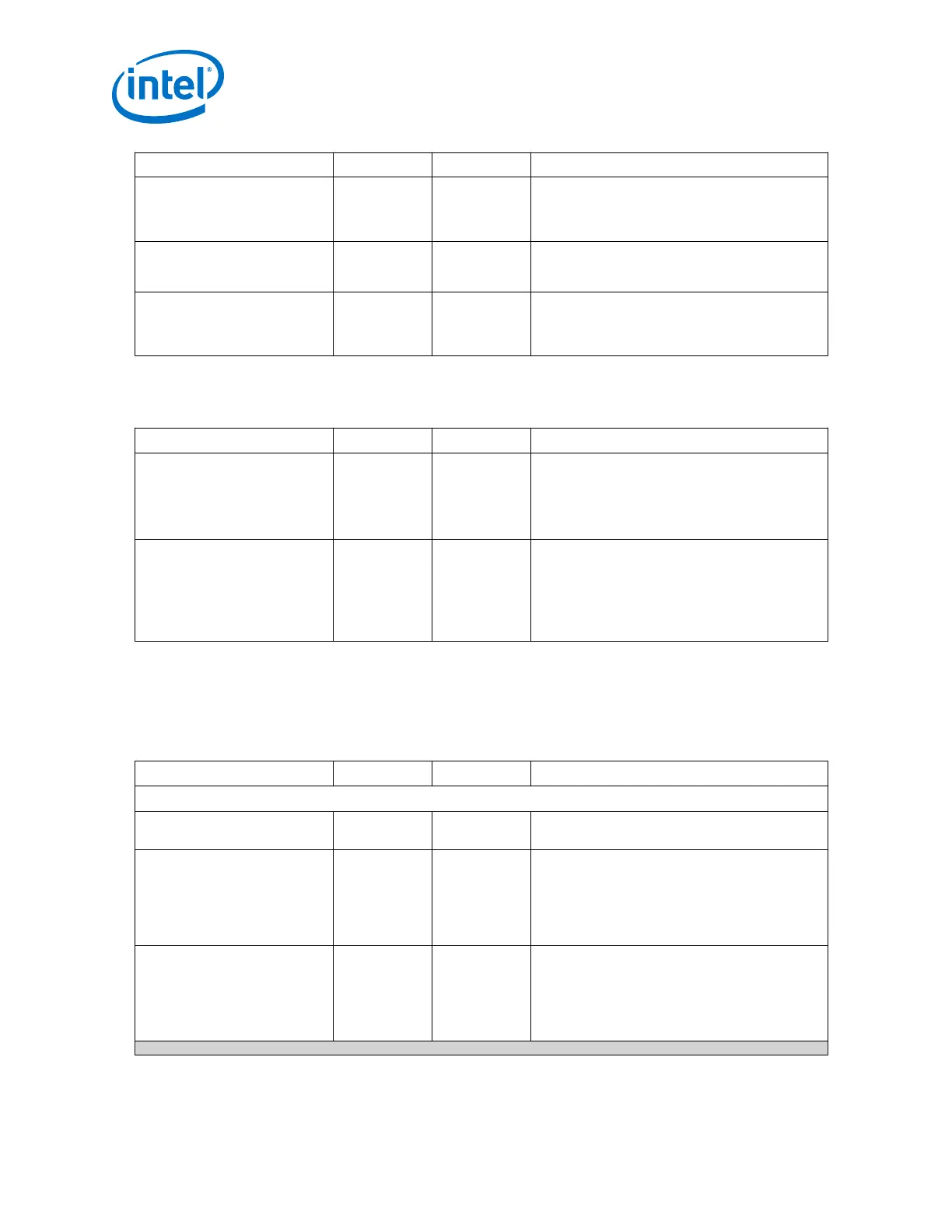

2.6.5.4.3. GMII Signals

The 16-bit TX and RX GMII supports 1GbE and 2.5GbE at 62.5 MHz and 156.25 MHz

respectively.

Table 160. GMII Signals

Signal Name Direction Width Description

TX GMII signals—synchronous to tx_clkout

gmii16b_tx_d

Input 16 TX data from the MAC. The MAC sends the lower

byte first followed by the upper byte.

gmii16b_tx_en

Input 2 When asserted, indicates the start of a new frame

from the MAC. Bit[0] corresponds to

gmii16b_tx_d[7:0]; bit[1] corresponds to

gmii16b_tx_d[15:8].

This signal remains asserted until the PHY receives

the last byte of the data frame.

gmii16b_tx_err

Input 2 When asserted, indicates an error. Bit[0]

corresponds to gmii16b_tx_err[7:0]; bit[1]

corresponds to gmii16b_tx_err[15:8].

The bits can be asserted at any time during a

frame transfer to indicate an error in the current

frame.

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

210

Loading...

Loading...