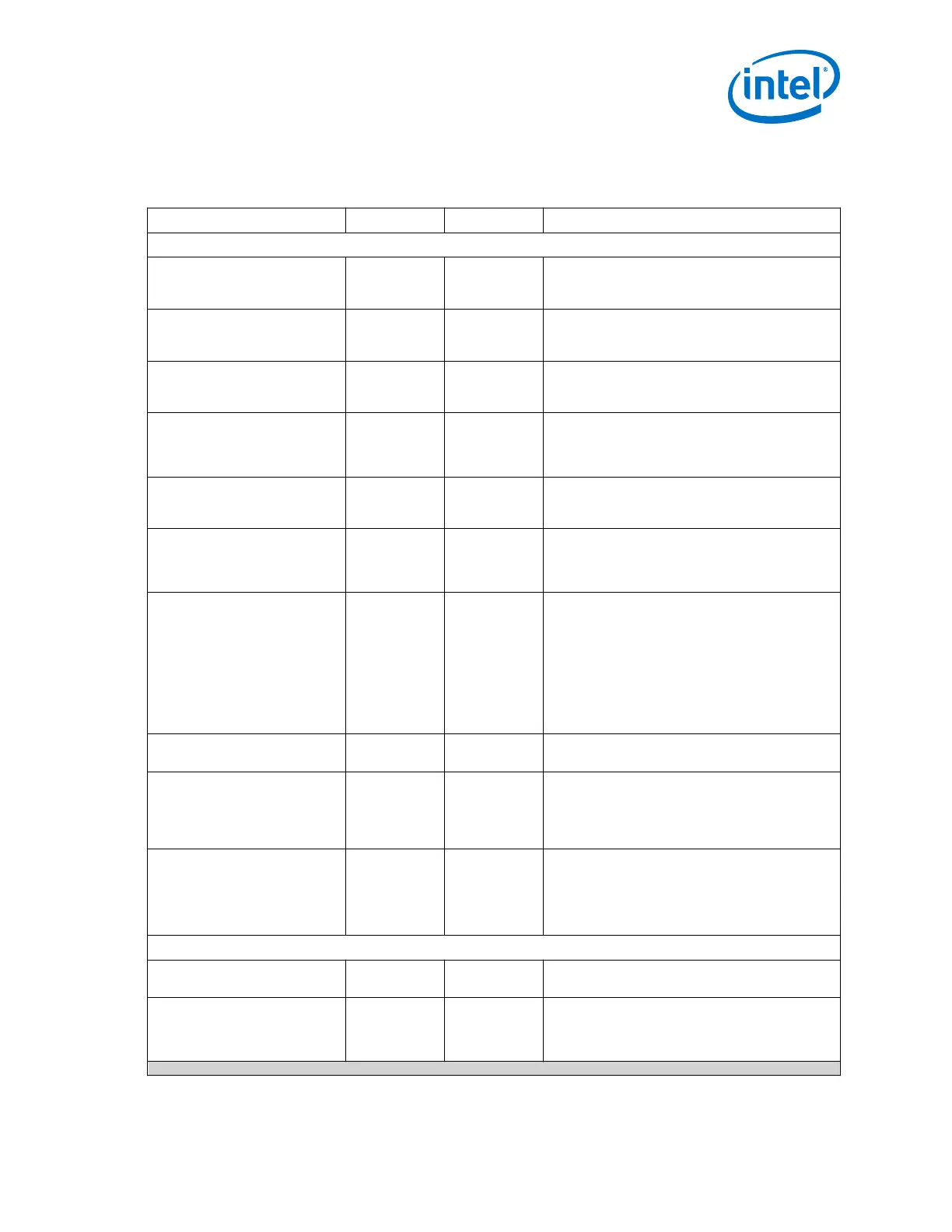

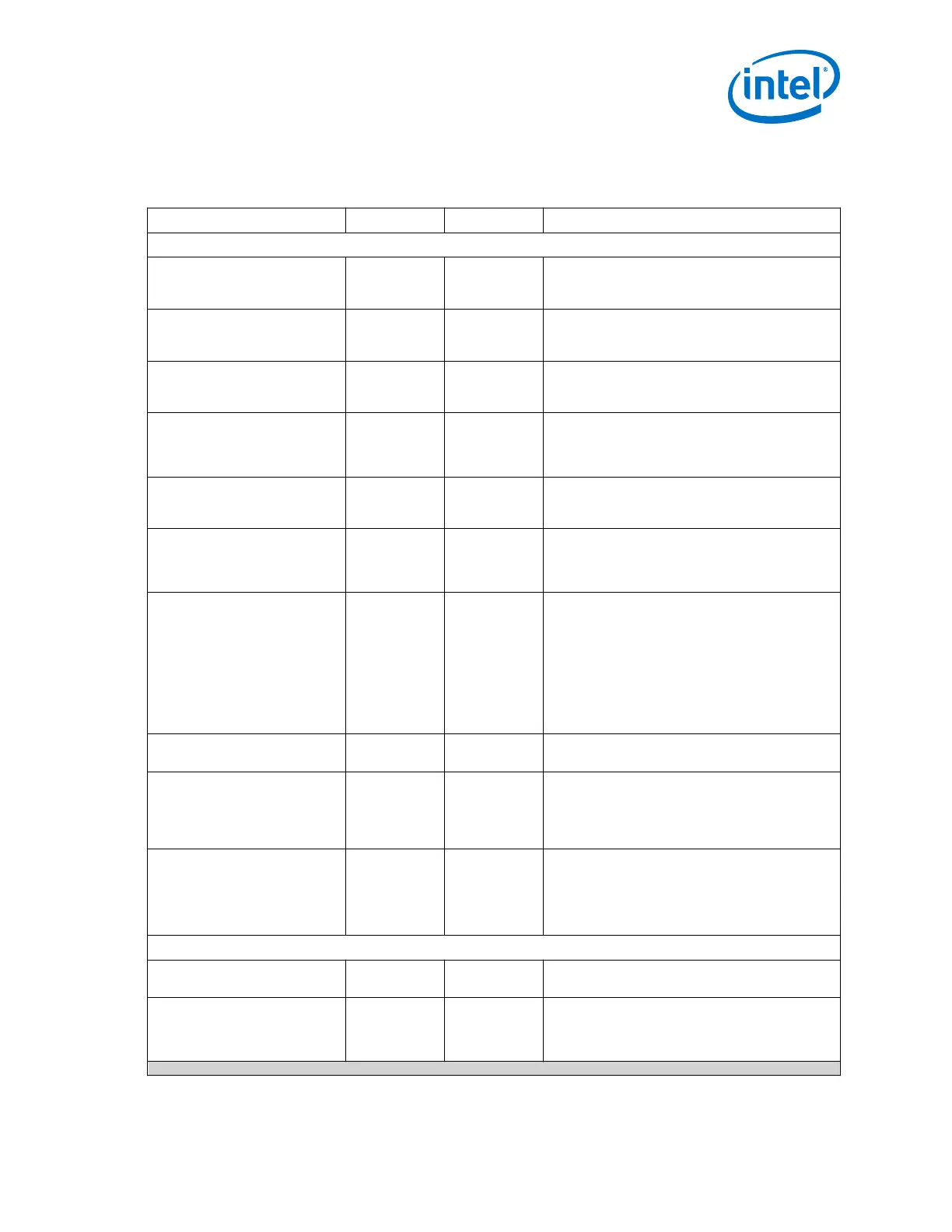

2.6.5.4.1. Clock and Reset Signals

Table 158. Clock and Reset Signals

Signal Name Direction Width Description

Clock signals

tx_clkout

Output 1 GMII TX clock, derived from

tx_serial_clk[1:0]. Provides 156.25 MHz

timing reference for 2.5GbE; 62.5 MHz for 1GbE.

rx_clkout

Output 1 GMII RX clock, derived from

tx_serial_clk[1:0]. Provides 156.25 MHz

timing reference for 2.5GbE; 62.5 MHz for 1GbE.

csr_clk

Input 1 Clock for the Avalon-MM control and status

interface. Intel recommends 125 – 156.25 MHz for

this clock.

xgmii_tx_coreclkin

Input 1 XGMII TX clock. Provides 156.25 MHz timing

reference for 10GbE and 312.5 MHz for 1G/

2.5G/5G/10G (USXGMII) mode. Synchronous to

tx_serial_clk with zero ppm.

xgmii_rx_coreclkin

Input 1 XGMII RX clock. Provides 156.25 MHz timing

reference for 10GbE and 312.5 MHz for 1G/

2.5G/5G/10G (USXGMII) mode.

latency_measure_clk

Input 1 Sampling clock for measuring the latency of the

16-bit GMII datapath. This clock operates at 80

MHz and is available only when the IEEE 1588v2

feature is enabled.

tx_serial_clk

Input 1-3 Serial clock from transceiver PLLs.

• 2.5GbE: Connect bit [0] to the transceiver PLL.

This clock operates at 1562.5 MHz.

• 1GbE: Connect bit [1] to the transceiver PLL.

This clock operates at 625 MHz.

• 10GbE: Connect bit [2] to the transceiver PLL.

This clock operates at 5156.25 MHz.

• 1G/2.5G/5G/10G (USXGMII) mode: Connect bit

[0] to 5156.25 MHz.

rx_cdr_refclk

Input 1 125-MHz RX CDR reference clock for 1GbE and

2.5GbE

rx_cdr_refclk_1

Input 1 RX CDR reference clock for 10GbE. The frequency

of this clock can be either 322.265625 MHz or

644.53125 MHz, as specified by the Reference

clock frequency for 10 GbE (MHz) parameter

setting.

rx_pma_clkout

Output 1 Recovered clock from CDR, operates at the

following frequency:

• 1GbE: 125 MHz

• 2.5GbE: 312.5 MHz

• 5GbE/10GbE: 322.265625 MHz

Reset signals

reset

Input 1 Active-high global reset. Assert this signal to

trigger an asynchronous global reset.

tx_analogreset

Input 1 Connect this signal to the Transceiver PHY Reset

Controller IP core. When asserted, triggers an

asynchronous reset to the analog block on the TX

path.

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

209

Loading...

Loading...