Table 156. Register Map

Address Range Usage Bit Configuration

0x00 : 0x1F 1000BASE-X/SGMII 16

2.5G, 1G/2.5G, 10M/

100M/1G/2.5, 10M/

100M/1G/2.5G/10G

(MGBASE-T), 1G/2.5G/10G

(MGBASE-T)

0x400 : 0x41F USXGMII 32 1G/2.5G/5G/10G (USXGMII)

0x461 Serial Loopback 32 1G/2.5G/5G/10G (USXGMII)

2.6.5.3.2. Definition: Register Access

Table 157. Types of Register Access

Access Definition

RO Read only.

RW Read and write.

RWC Read, and write and clear. The user application writes 1 to the register bit(s) to invoke a defined

instruction. The IP core clears the bit(s) upon executing the instruction.

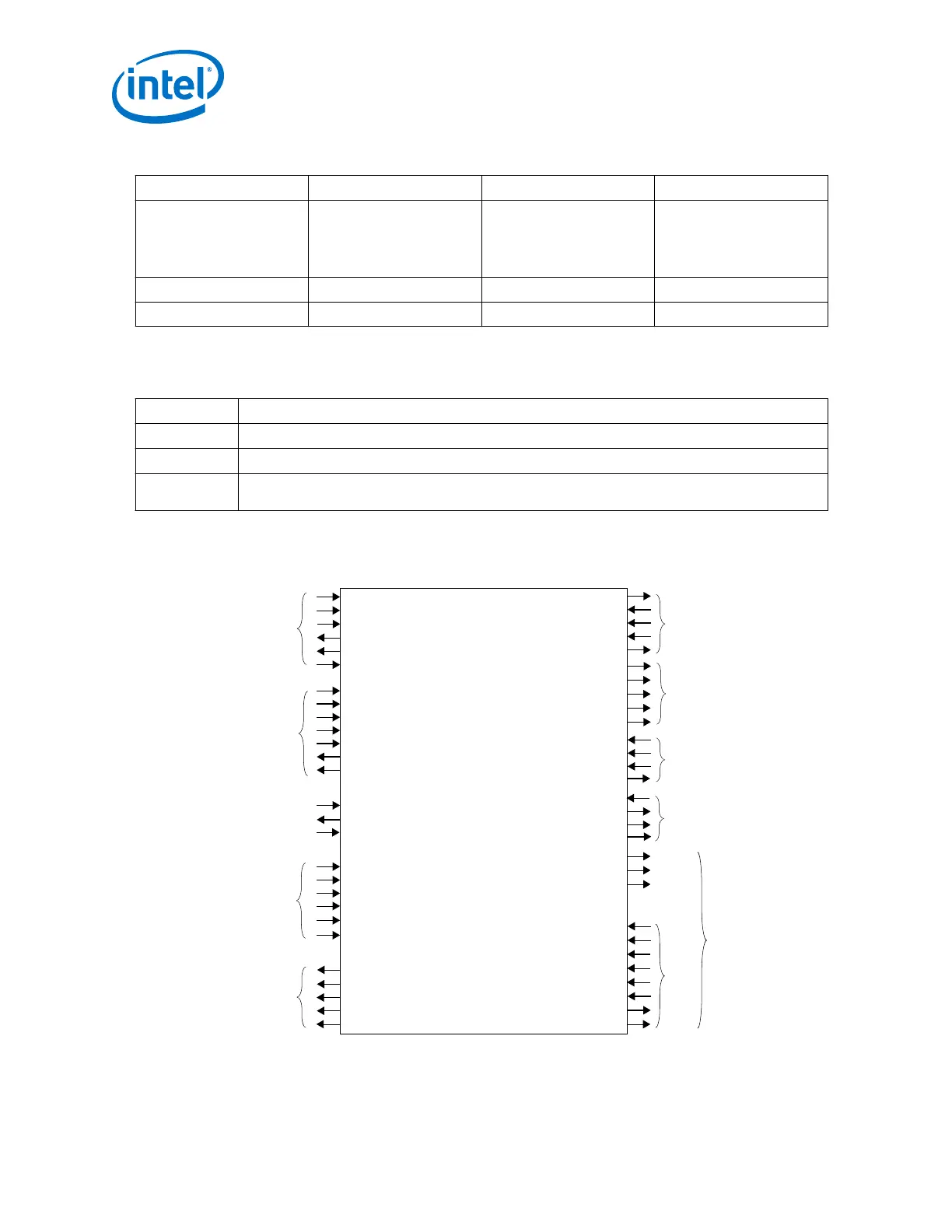

2.6.5.4. Interface Signals

Figure 80. PHY Interface Signals

PHY

reset

pll_powerdown

tx_digitalreset

rx_digitalreset

tx_analogreset

rx_analogreset

Reset

csr_clk

csr_address[4:0]

csr_write

csr_read

csr_writedata[] (i)

csr_readdata[] (i)

csr_waitrequest

Avalon-MM

Control & Status

Interface

rx_is_lockedtodata

tx_cal_busy

rx_cal_busy

Transceiver Status &

Reconfiguration Interface

reconfig_clk

reconfig_write

reconfig_address[9:0]

reconfig_reset

reconfig_readdata[31:0]

reconfig_writedata[31:0]

reconfig_read

reconfig_waitrequest

Arria 10

xcvr_mode[1:0]

operating_speed[2:0]

latency_measure_clk

gmii16b_tx_d[15:0]

gmii16b_tx_en[1:0]

gmii16b_tx_err[1:0]

tx_clkout

TX GMII

gmii16b_tx_latency[21:0]

rx_clkout

RX GMII

gmii16b_rx_d[15:0]

gmii16b_rx_dv[1:0]

gmii16b_rx_err[1:0]

gmii16b_rx_latency[21:0]

xgmii_tx_control[7:0]

xgmii_tx_data[63:0]

xgmii_tx_coreclkin

TX XGMII

xgmii_rx_control[7:0]

xgmii_rx_data[63:0]

xgmii_rx_coreclkin

RX XGMII

led_link

led_char_err

led_disp_err

Status

Interface

led_an

rx_block_lock

tx_serial_clk

rx_cdr_refclk

tx_serial_data

rx_serial_data

Serial

Interface

rx_cdr_refclk1

rx_pma_clkout

xgmii_tx_valid

xgmii_rx_valid

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

208

Loading...

Loading...