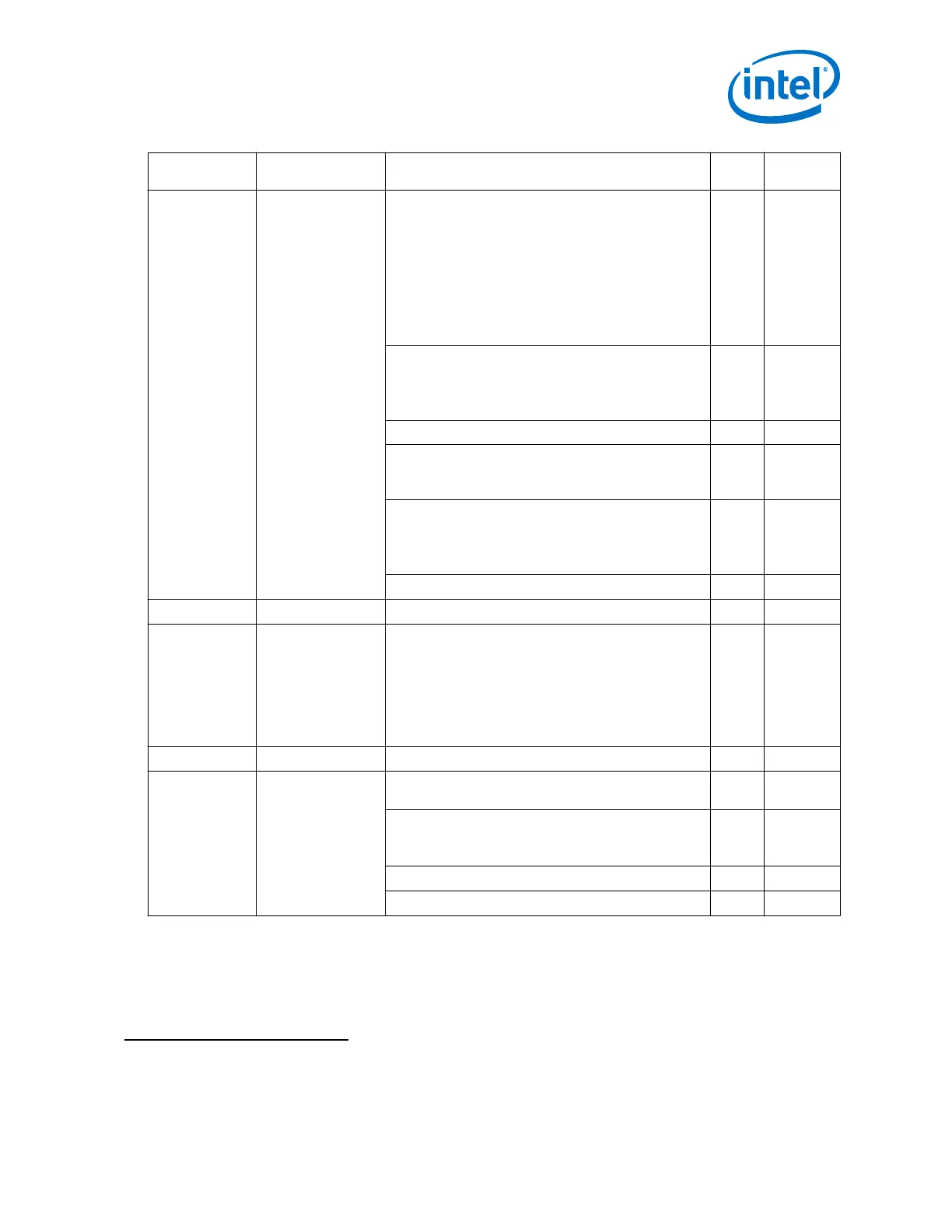

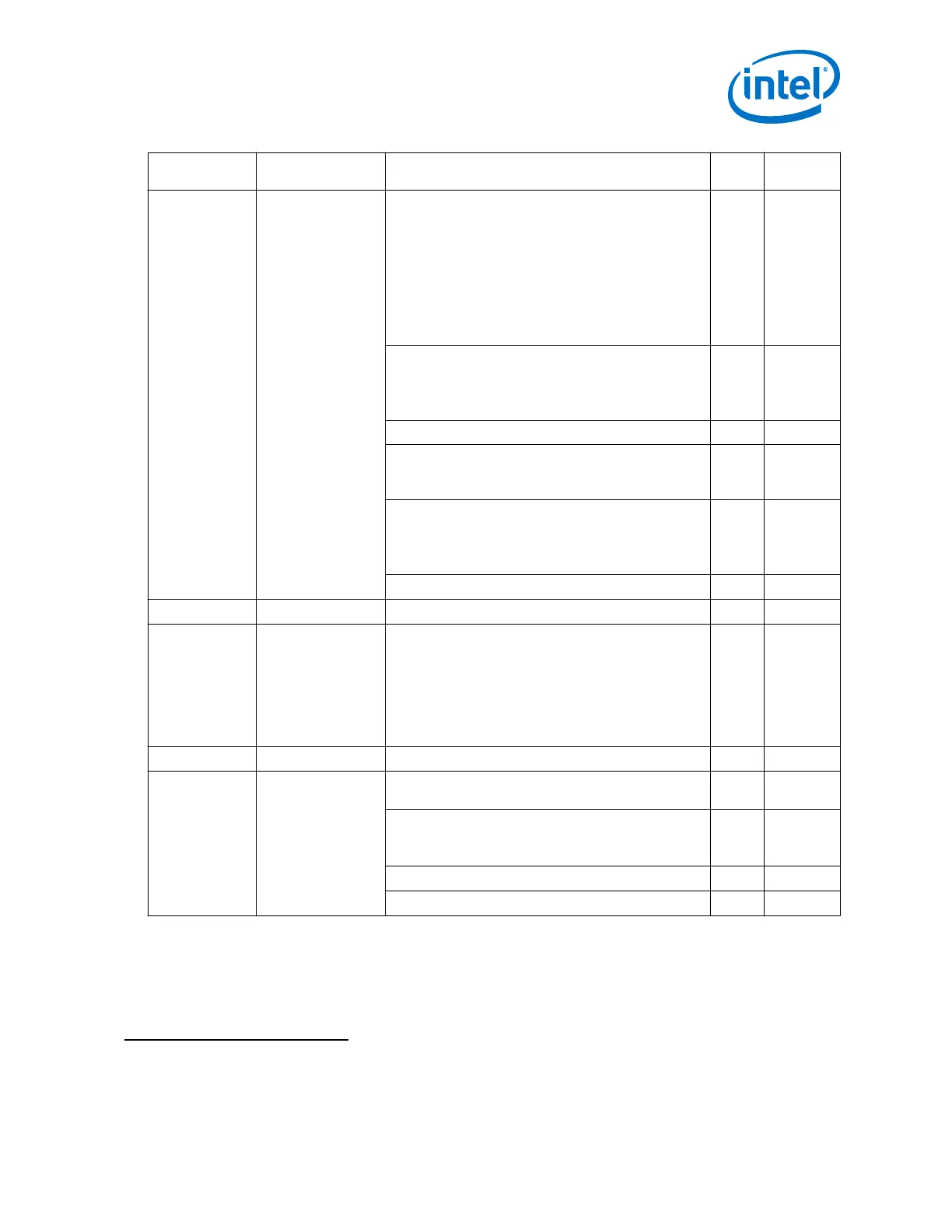

Addr Name Description Access HW Reset

Value

Bit [11:9]: SPEED

• 3'b000: 10M

• 3'b001: 100M

• 3'b010: 1G

• 3'b011: 10G

• 3'b100: 2.5G

• 3'b101: 5G

• 3'b110: Reserved

• 3'b111: Reserved

RO 0x0

Bit [12]: DUPLEX

Indicates the duplex mode.

• 0: Half duplex

• 1: Full duplex

RO 0x0

Bit [13]: Reserved — —

Bit [14]: ACKNOWLEDGE

A value of 1 indicates that the device has received three

consecutive matching ability values from its link partner.

RO 0x0

Bit [15]: LINK

Indicates the link status.

• 0: Link down

• 1: Link up

RO 0x0

Bit [31:16]: Reserved — —

0x406:0x411 Reserved — — —

0x412

usxgmii_link_tim

er

Auto-Negotiation link timer. Sets the link timer value in

bit [19:14] from 0 to 2 ms in approximately 0.05-ms

steps. You must program the link timer to ensure that it

matches the link timer value of the external NBASE-T

PHY IP Core.

The reset value sets the link timer to approximately 1.6

ms.

Bits [13:0] are reserved and always set to 0.

[19:14

]: RW

[13:0]:

RO

[19:14]:

0x1F

[13:0]:

0x0

0x413:0x41F Reserved — — —

0x461

phy_serial_loopb

ack

Configures the transceiver serial loopback in the PMA

from TX to RX.

— —

Bit [0]

• 0: Disables the PHY serial loopback

• 1: Enables the PHY serial loopback

RW 0x0

Bit [15:1]: Reserved — —

Bit [31:16]: Reserved — —

2.6.5.3.1. Register Map

You can access the 16-bit/32-bit configuration registers

(37)

via the Avalon-MM

interface.

(37)

These registers are identical to the Intel Arria 10 variation of 1G/2.5G/5G/10G Multi-rate

Ethernet PHY IP core.

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

207

Loading...

Loading...