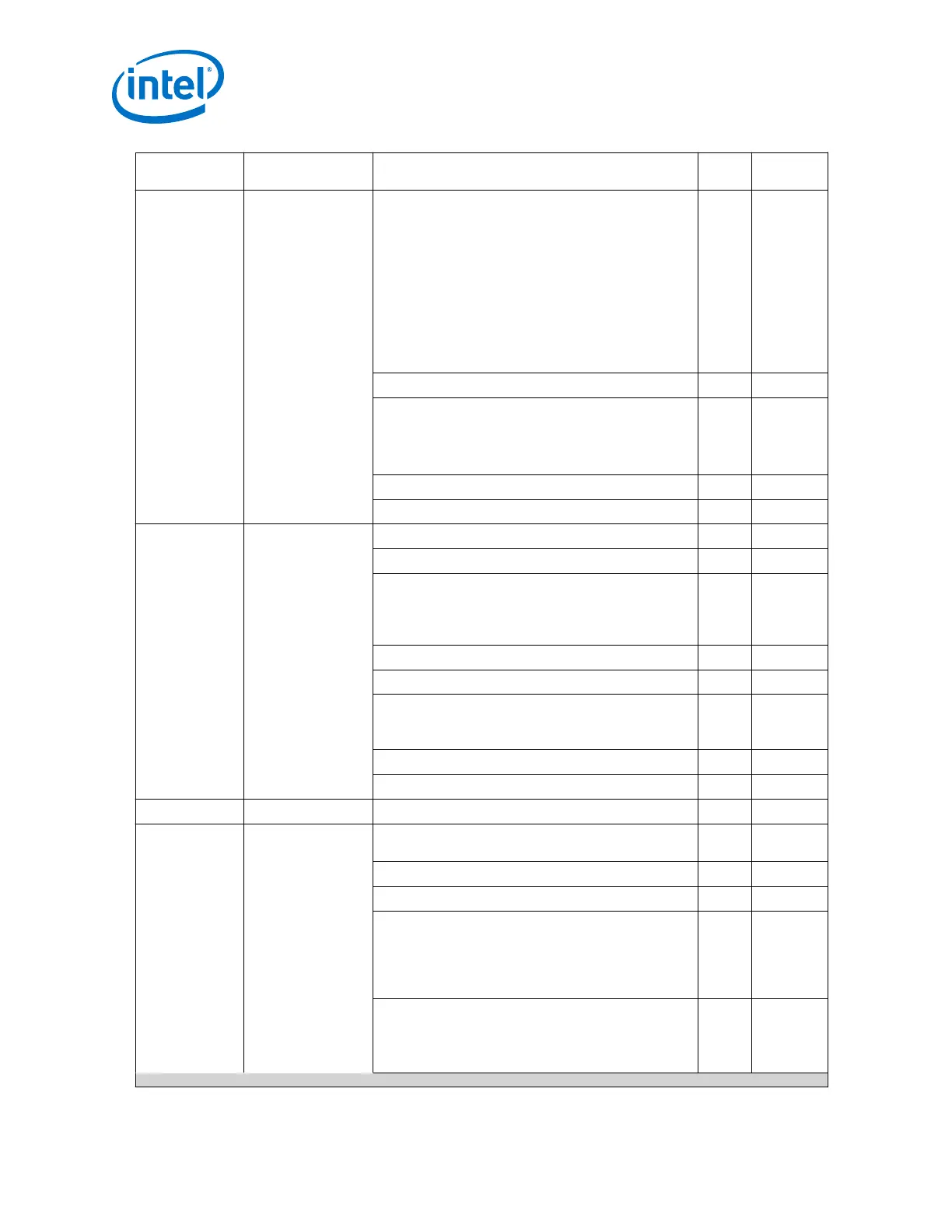

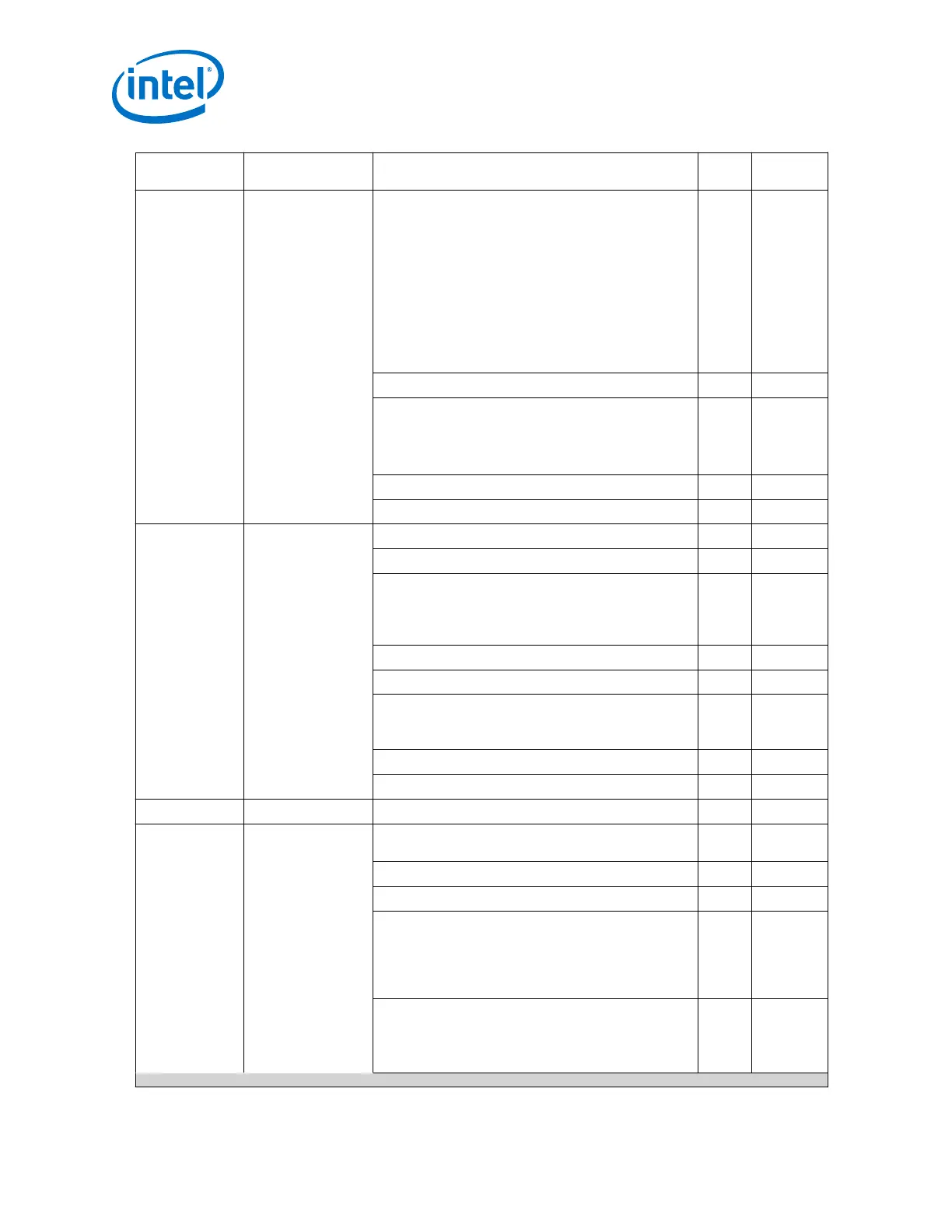

Addr Name Description Access HW Reset

Value

Bit [4:2]: USXGMII_SPEED is the operating speed of

the PHY in USXGMII mode and USE_USXGMII_AN is set

to 0.

• 3’b000: Reserved

• 3’b001: Reserved

• 3’b010: 1G

• 3’b011: 10G

• 3’b100: 2.5G

• 3’b101: 5G

• 3’b110: Reserved

• 3’b111: Reserved

RW 0x0

Bit [8:5]: Reserved — —

Bit [9]: RESTART_AUTO_NEGOTIATION

Write 1 to restart Auto-Negotiation sequence The bit is

cleared by hardware when Auto-Negotiation is

restarted.

RWC

(hardw

are

self-

clear)

0x0

Bit [15:10]: Reserved — —

Bit [30:16]: Reserved — —

0x401

usxgmii_status

Status Register — —

Bit [1:0]: Reserved — —

Bit [2]: LINK_STATUS indicates link status for USXGMII

all speeds

• 1: Link is established

• 0: Link synchronization is lost, a 0 is latched

RO 0x0

Bit [3]: Reserved — —

Bit [4]: Reserved — —

Bit [5]: AUTO_NEGOTIATION_COMPLETE

A value of 1 indicates the Auto-Negotiation process is

completed.

RO 0x0

Bit [15:6]: Reserved — —

Bit [31:16]: Reserved — —

0x402:0x404 Reserved — — —

0x405

usxgmii_partner_

ability

Device abilities advertised to the link partner during

Auto-Negotiation

— —

Bit [0]: Reserved — —

Bit [6:1]: Reserved — —

Bit [7]: EEE_CLOCK_STOP_CAPABILITY

Indicates whether or not energy efficient ethernet (EEE)

clock stop is supported.

• 0: Not supported

• 1: Supported

RO 0x0

Bit [8]: EEE_CAPABILITY

Indicates whether or not EEE is supported.

• 0: Not supported

• 1: Supported

RO 0x0

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

206

Loading...

Loading...