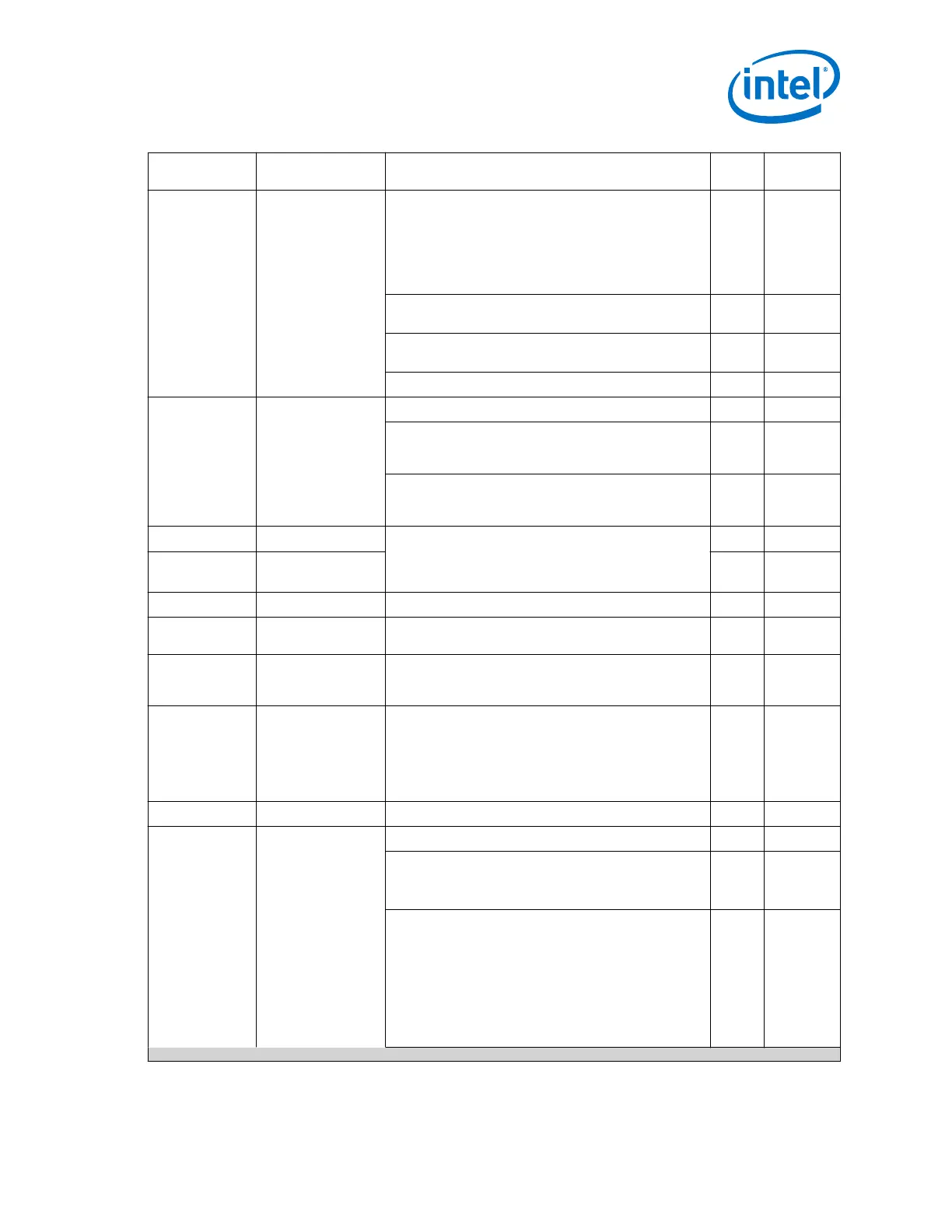

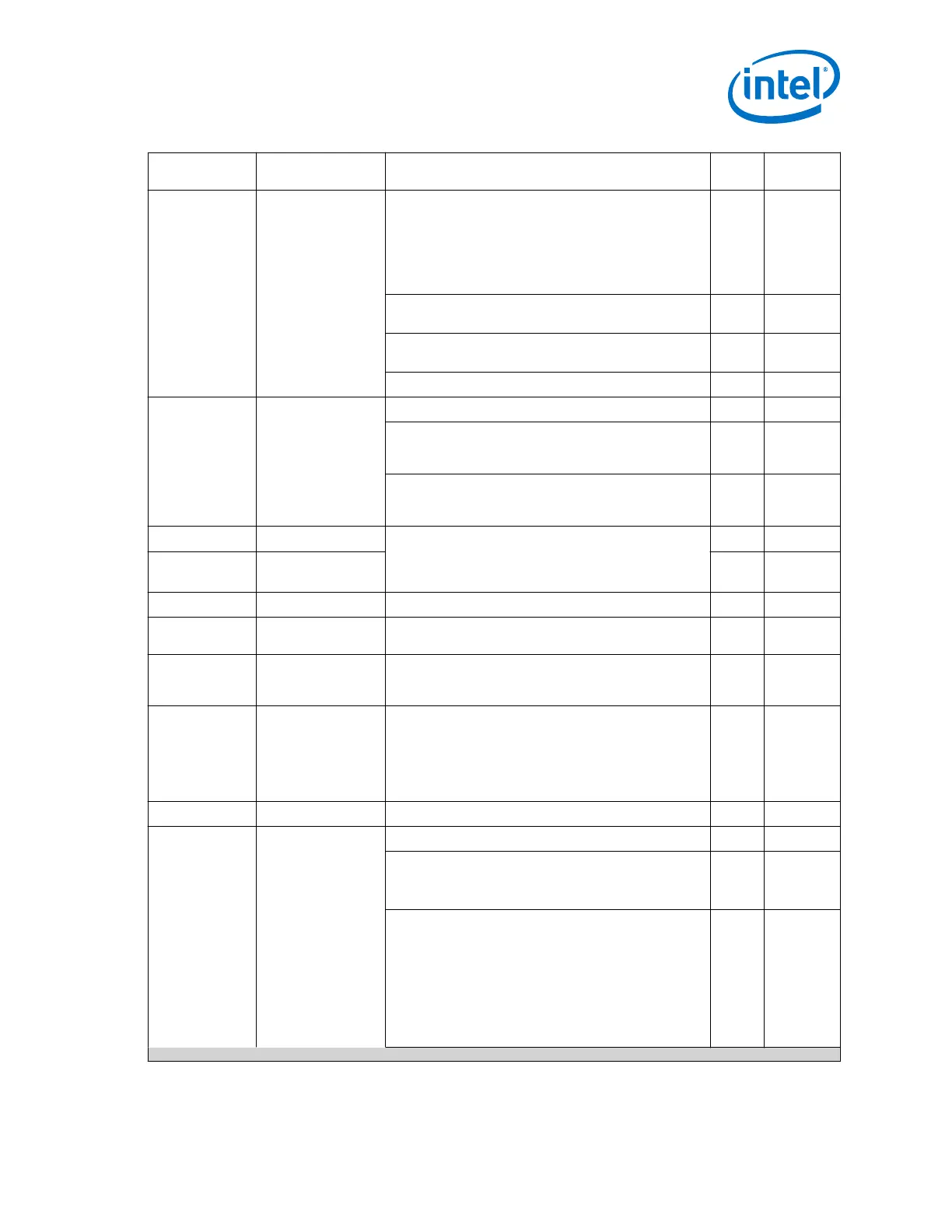

Addr Name Description Access HW Reset

Value

•

Bits [8:7]: PS. The PAUSE support.

— 00: No PAUSE.

— 01: Symmetric PAUSE.

— 10: Asymmetric PAUSE towards the link partner.

— 11: Asymmetric and symmetric PAUSE towards

the link device.

RO 0

•

Bit [6]: HD. A value of "1" indicates that half-duplex

is supported.

RO 0

•

Bit [5]: FD. A value of "1" indicates that full-duplex

is supported.

RO 0

• The rest of the bits are reserved. — —

0x06

an_expansion

The PCS capabilities and auto-negotiation status. — —

Bit [1]: PAGE_RECEIVE. A value of "1" indicates that

the partner_ability register has been updated. This bit is

automatically cleared once it is read.

RO 0

Bit [0]: LINK_PARTNER_AUTO_NEGOTIATION_ABLE. A

value of "1" indicates that the link partner supports

auto-negotiation.

RO 0

0x07

device_next_page

The PHY does not support the next page feature. These

registers are always set to 0.

RO 0

0x08

partner_next_pag

e

RO 0

0x09:0x0F Reserved — — —

0x10

scratch

Provides a memory location to test read and write

operations.

RW 0

0x11

rev

The current version of the PHY IP core. RO Current

version of

the PHY

0x12:0x13

link_timer

21-bit auto-negotiation link timer.

• Offset 0x12: link_timer[15:0]. Bits [8:0] are always

be set to 0.

• Offset 0x13: link_timer[20:16] occupies the lower 5

bits. The remaining 11 bits are reserved and must

always be set to 0.

RW 0

0x14:0x1F Reserved — — —

0x400

usxgmii_control

Control Register — —

Bit [0]: USXGMII_ENA:

• 0: 10GBASE-R mode

• 1: USXGMII mode

RW 0x0

Bit [1]: USXGMII_AN_ENA is used when USXGMII_ENA

is set to 1:

• 0: Disables USXGMII Auto-Negotiation and manually

configures the operating speed with the

USXGMII_SPEED register.

• 1: Enables USXGMII Auto-Negotiation, and

automatically configures operating speed with link

partner ability advertised during USXGMII Auto-

Negotiation.

RW 0x1

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

205

Loading...

Loading...