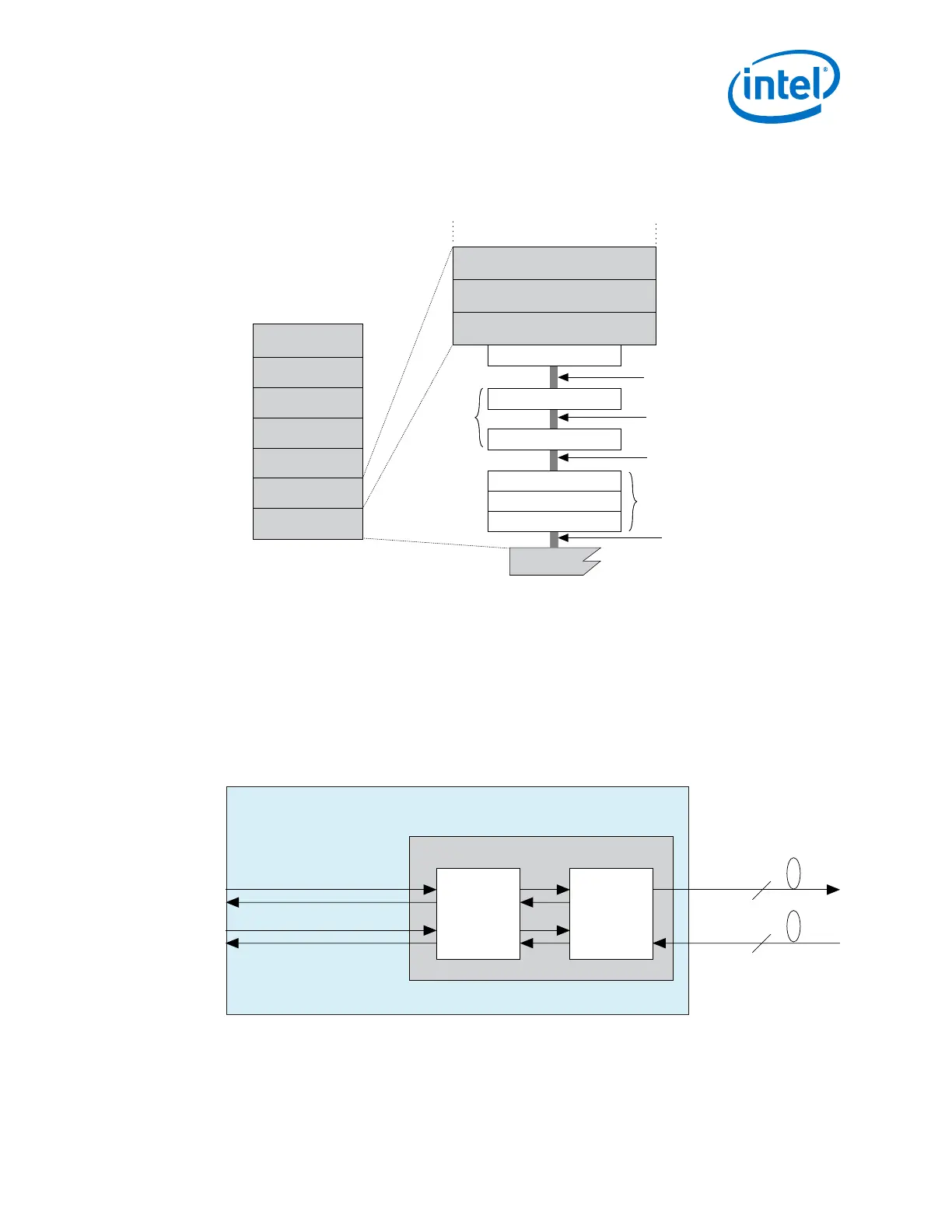

Figure 81. XAUI and XGMII Layers

OSI

Reference

Model Layers

Application

Presentation

Session

Transport

Network

Data Link

Physical

PMA

PMD

Medium

10 Gbps

Optional

XGMII

Extender

Physical Layer Device

MAC Control (Optional)

Logical Link Control (LLC)

LAN Carrier Sense Multiple

Access/Collision Detect (CSMA/CD)

Layers

Higher Layers

Reconciliation

Media Access Control (MAC)

PCS

10 Gigabit Media Independent Interface

XGMII Extender Sublayer

XGMII Extender Sublayer

10 Gigabit Attachment Unit Interface

10 Gigabit Media Independent Interface

Medium Dependent Interface

Intel's XAUI PHY IP core implements the IEEE 802.3 Clause 48 specification to extend

the operational distance of the XGMII interface and reduce the number of interface

signals.

XAUI extends the physical separation possible between the 10 Gbps Ethernet MAC

function and the Ethernet standard PHY component to one meter. The XAUI PHY IP

core accepts 72-bit data (single data rate–SDR XGMII) from the application layer at

156.25 Mbps. The serial interface runs at 4 × 3.125 Gbps.

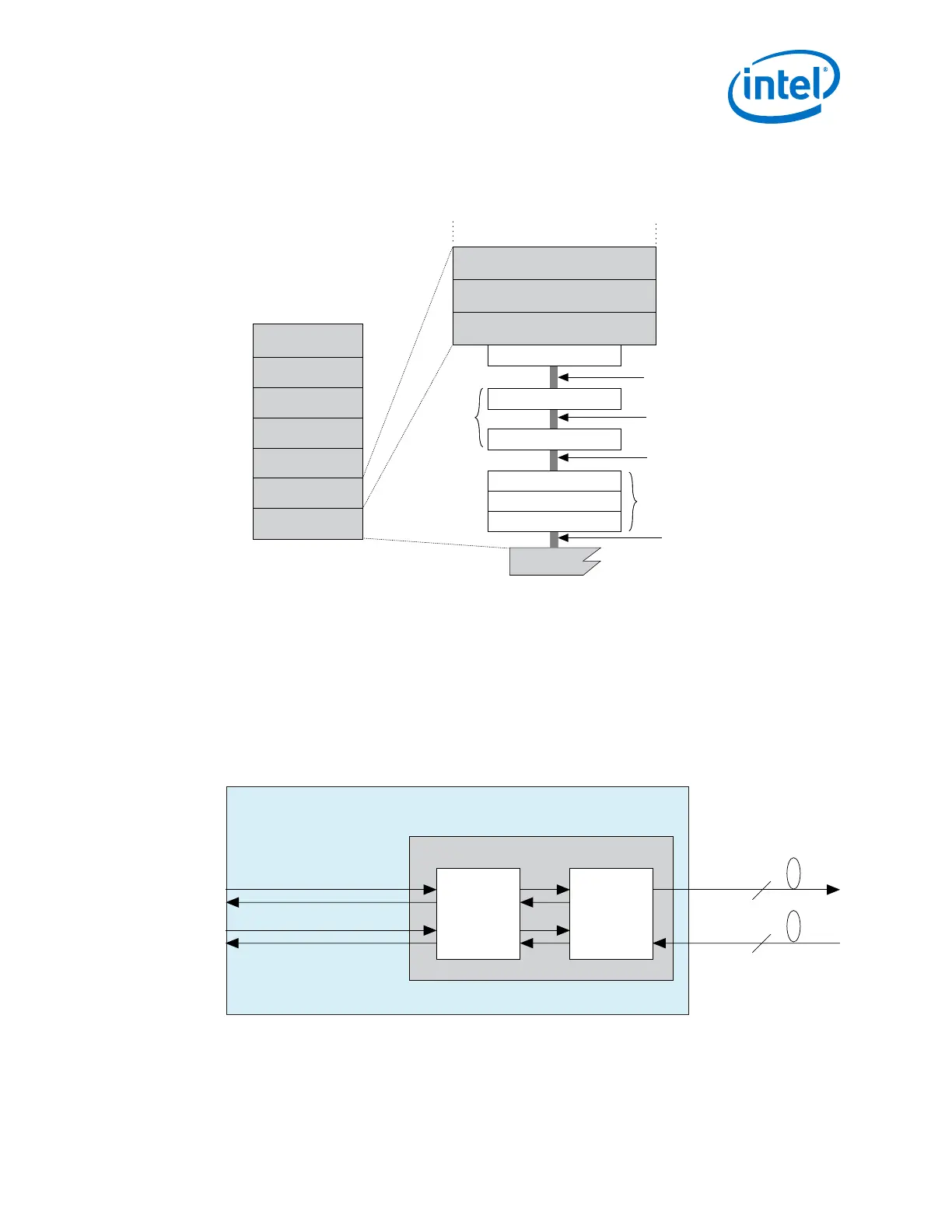

Figure 82. XAUI PHY IP Core

XAUI PHY IP Core

4 x 3.125 Gbps serial

XAUI PHY IP

Hard PMA

PCS

8B/10B

Word Aligner

Phase Comp

SDR XGMII

72 bits @ 156.25 Mbps

Avalon-MM

Control & Status

4

4

Intel's third-party IP partner for Dual Data Rate XAUI (DDR XAUI or DXAUI) and

Reduced XAUI (RXAUI) support is MorethanIP (MTIP).

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

215

Loading...

Loading...