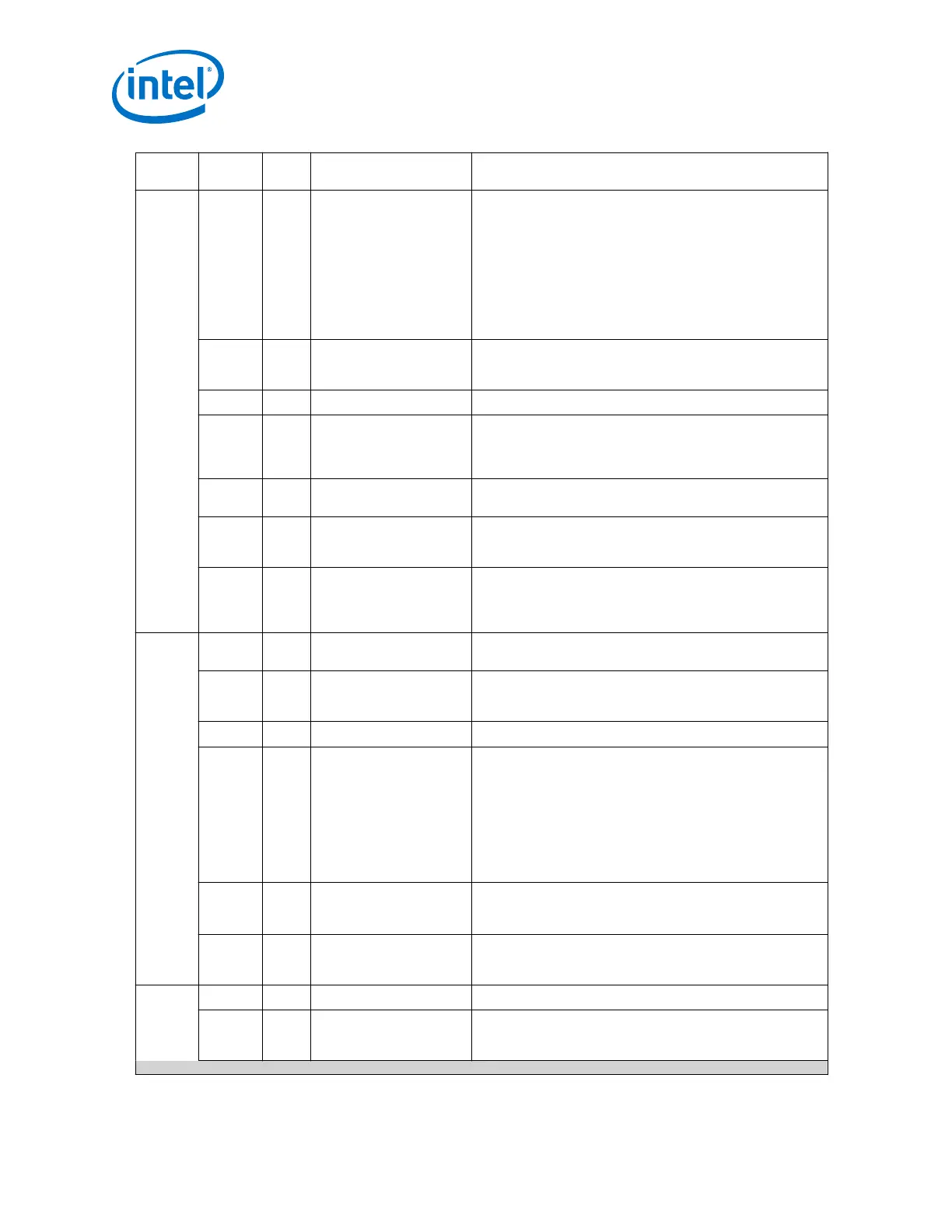

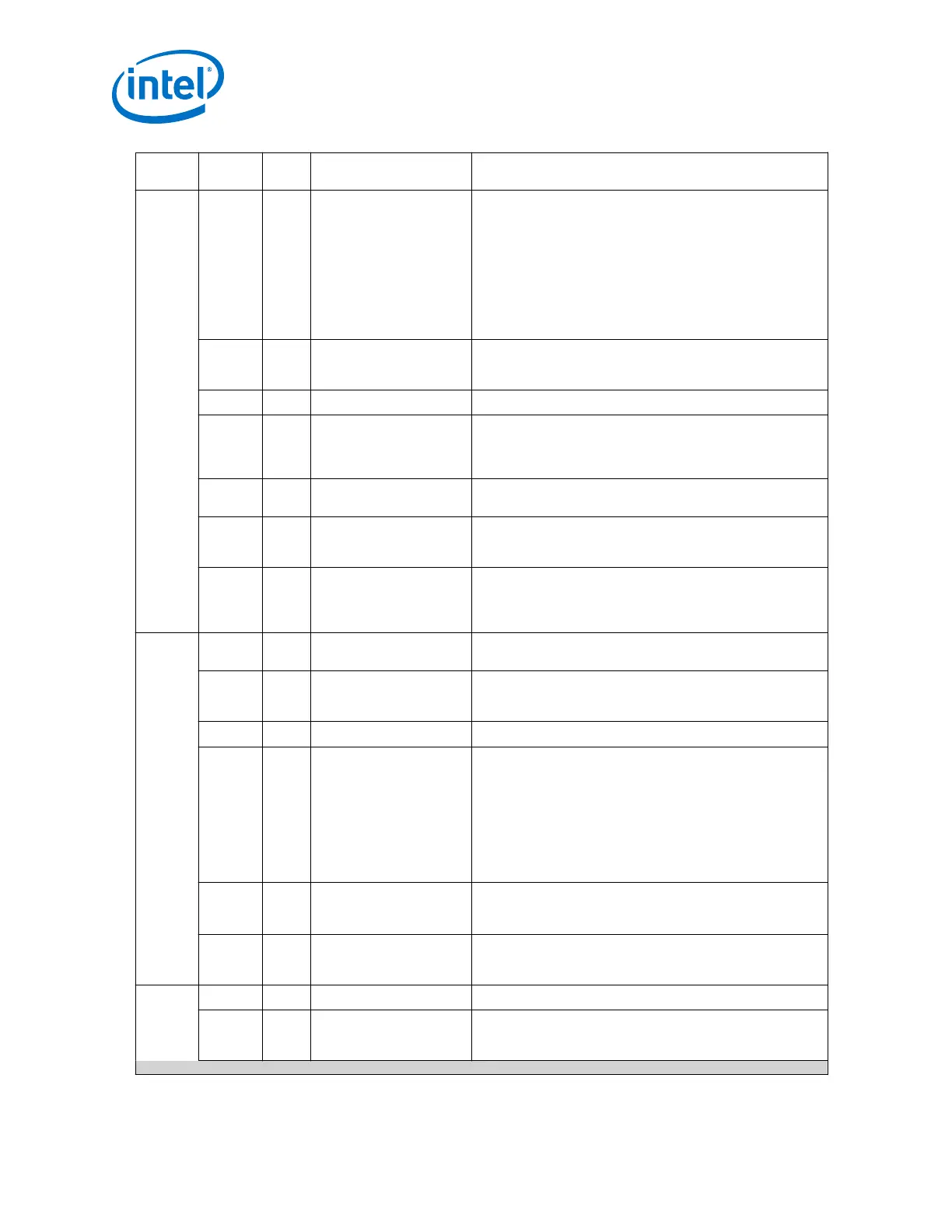

Word

Addr

Bit R/W Name Description

7:4 RW

SEQ Force Mode[3:0]

Forces the sequencer to a specific protocol. Must write the

Reset SEQ bit to 1 for the Force to take effect. The following

encodings are defined:

• 0000: No force

• 0001: GigE

• 0010: XAUI

• 0100: 10GBASE-R

• 0101: 10GBASE-KR

• 1100: 10GBASE-KR FEC

8 RW

Enable Arria 10

Calibration

When set to 1, it enables the Arria 10 HSSI reconfiguration

calibration as part of the PCS dynamic reconfiguration. 0 skips

the calibration when the PCS is reconfigured.

11:9 RW Reserved —

12 RW

LT failure response

When set to 1, LT failure causes the PHY to go into data

mode. When set to 0, LT failure restarts auto-negotiation (if

enabled). If auto-negotiation is not enabled, the PHY restarts

LT.

16 RW

KR FEC enable 171.0

When set to 1, FEC is enabled. When set to 0, FEC is

disabled. Resets to the CAPABLE_FEC parameter value.

17 RW

KR FEC enable err

ind 171.1

When set to 1, KR PHY FEC decoding errors are signaled to

the PCS. When set to 0, FEC errors are not signaled to the

PCS. See Clause 74.8.3 of IEEE 802.3ap-2007 for details.

18 RW

KR FEC request

When set to 1, enables the FEC request. When this bit

changes, you must assert the Reset SEQ bit (0x4B0[0]) to

renegotiate with the new value. When set to 0, disables the

FEC request.

0x4B1 0 R

SEQ Link Ready

When asserted, the sequencer is indicating that the link is

ready.

1 R

SEQ AN timeout

When asserted, the sequencer has had an Auto Negotiation

timeout. This bit is latched and is reset when the sequencer

restarts Auto Negotiation.

2 R

SEQ LT timeout

When set, indicates that the Sequencer has had a timeout.

13:8 R

SEQ Reconfig

Mode[5:0]

Specifies the Sequencer mode for PCS reconfiguration. The

following modes are defined:

• Bit 8, mode[0]: AN mode

• Bit 9, mode[1]: LT Mode

• Bit 10, mode[2]: 10G data mode

• Bit 11, mode[3]: GigE data mode

• Bit 12, mode[4]: Reserved for XAUI

• Bit 13, mode[5]: 10G FEC mode

16 R

KR FEC ability 170.0

When set to 1, indicates that the 10GBASE-KR PHY supports

FEC. Set as parameter SYNTH_FEC. For more information,

refer to Clause 45.2.1.84 of IEEE 802.3ap-2007.

17 R

KR FEC err ind

ability 170.0

When set to 1, indicates that the 10GBASE-KR PHY is capable

of reporting FEC decoding errors to the PCS. For more

information, refer to Clause 74.8.3 of IEEE 802.3ap-2007.

0x4B2 0:10 — Reserved —

11 RW

KR FEC TX Error

Insert

Writing a 1 inserts one error pulse into the TX FEC depending

on the Transcoder and Burst error settings. This bit self

clears.

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

150

Loading...

Loading...