Related Information

• Arria 10 Standard PCS Architecture on page 479

For more information about Standard PCS architecture

• Arria 10 PMA Architecture on page 447

For more information about PMA architecture

• Using PLLs and Clock Networks on page 398

For more information about implementing PLLs and clocks

• PLLs on page 349

PLL architecture and implementation details

• Resetting Transceiver Channels on page 416

Reset controller general information and implementation details

• Standard PCS Ports on page 86

Port definitions for the Transceiver Native PHY Standard Datapath

2.9.2.17. Native PHY IP Parameter Settings for Basic, Basic with Rate Match

Configurations

This section contains the recommended parameter values for this protocol. Refer to

Using the Arria 10 Transceiver Native PHY IP Core for the full range of parameter

values.

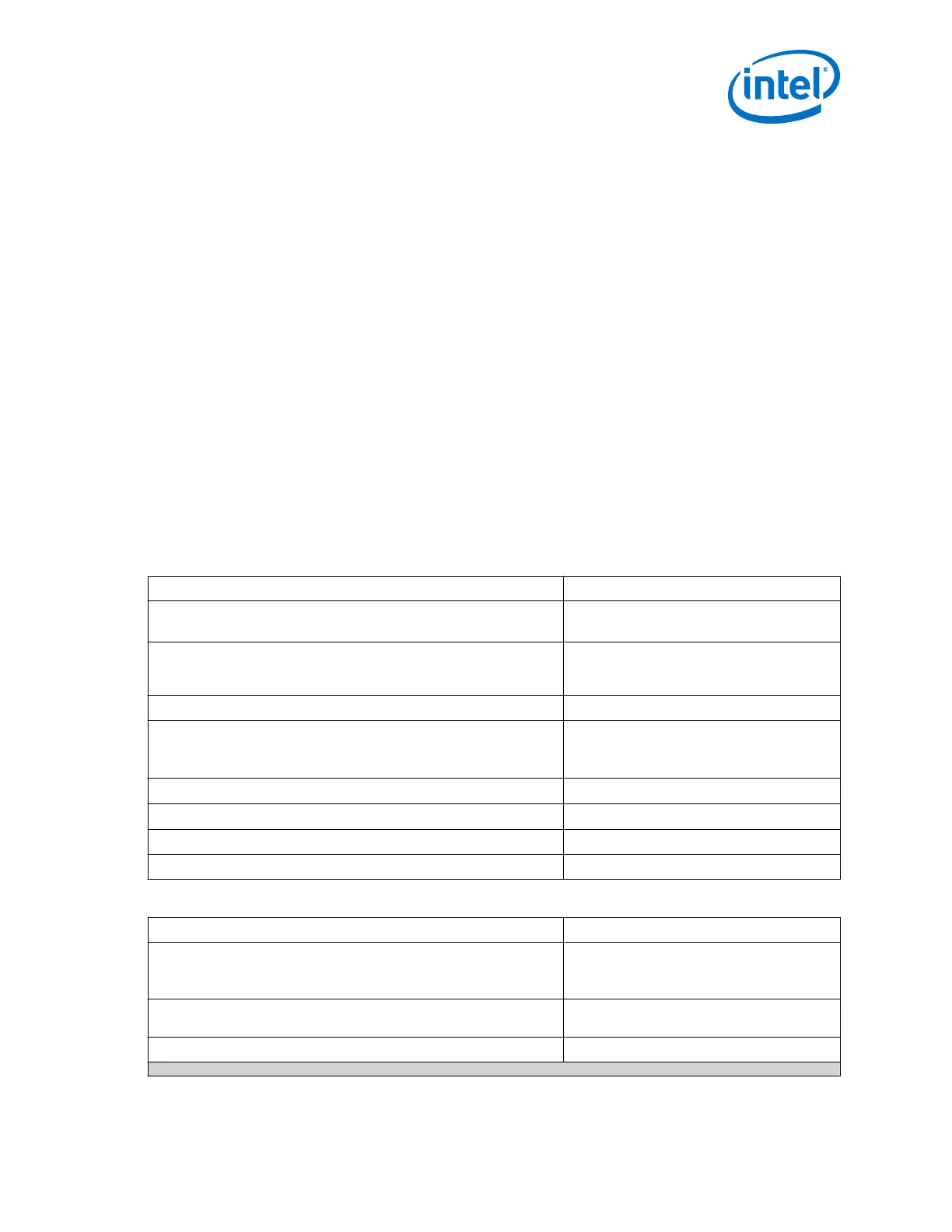

Table 217. General and Datapath Options Parameters

Parameter Range

Message level for rule violations

error

warning

Transceiver configuration rules

Basic/Custom (Standard PCS)

Basic/Custom w/Rate Match (Standard

PCS)

PMA configuration rules basic

Transceiver mode

TX/RX Duplex

TX Simplex

RX Simplex

Number of data channels

1 to 96

Data rate

611 Mbps to 12 Gbps

Enable datapath and interface reconfiguration On/Off

Enable simplified data interface On/Off

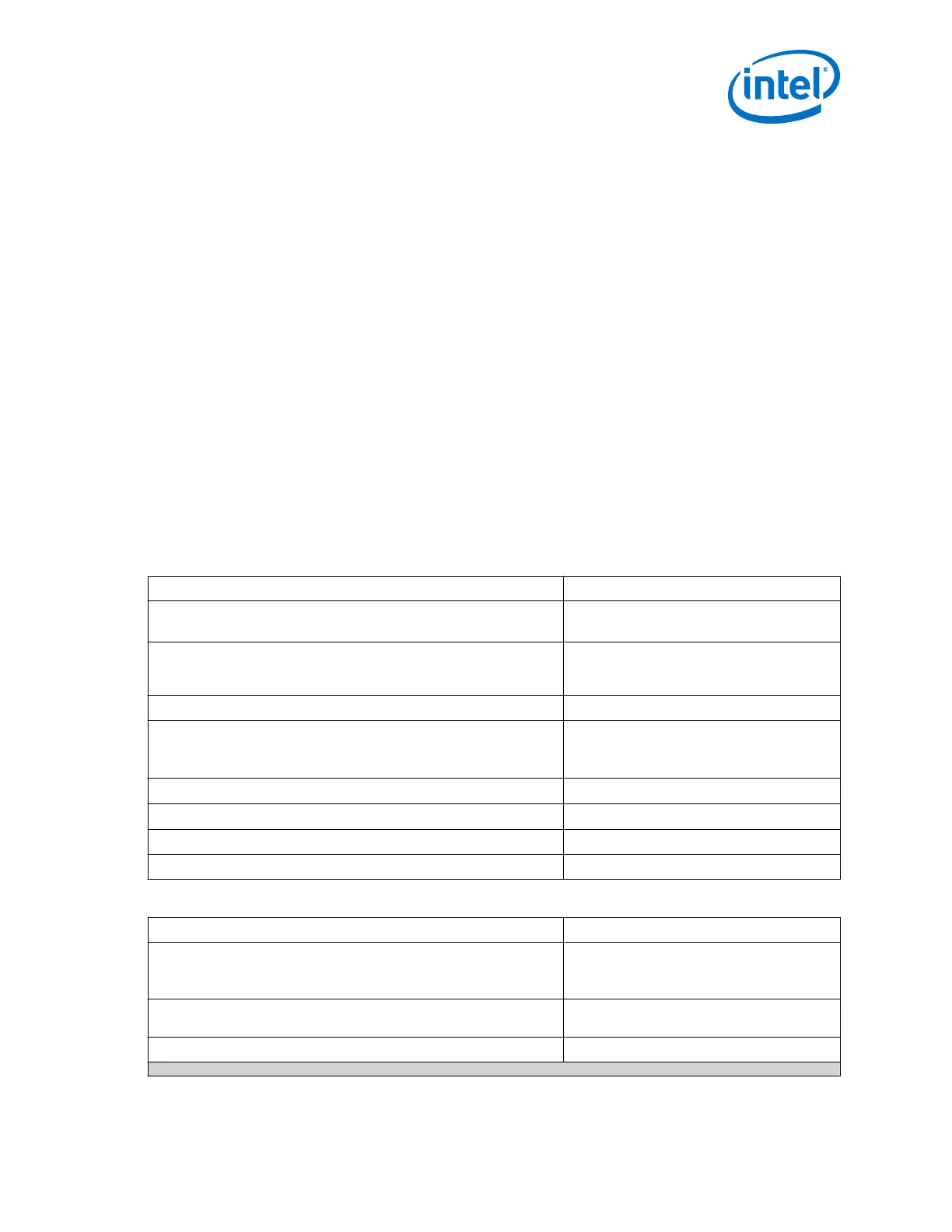

Table 218. TX PMA Parameters

Parameter Range

TX channel bonding mode Not bonded

PMA-only bonding

PMA and PCS bonding

PCS TX channel bonding master Auto, n-1 (where n = the number of data

channels)

Actual PCS TX channel bonding master n-1 (where n = the number of data channels)

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

315

Loading...

Loading...