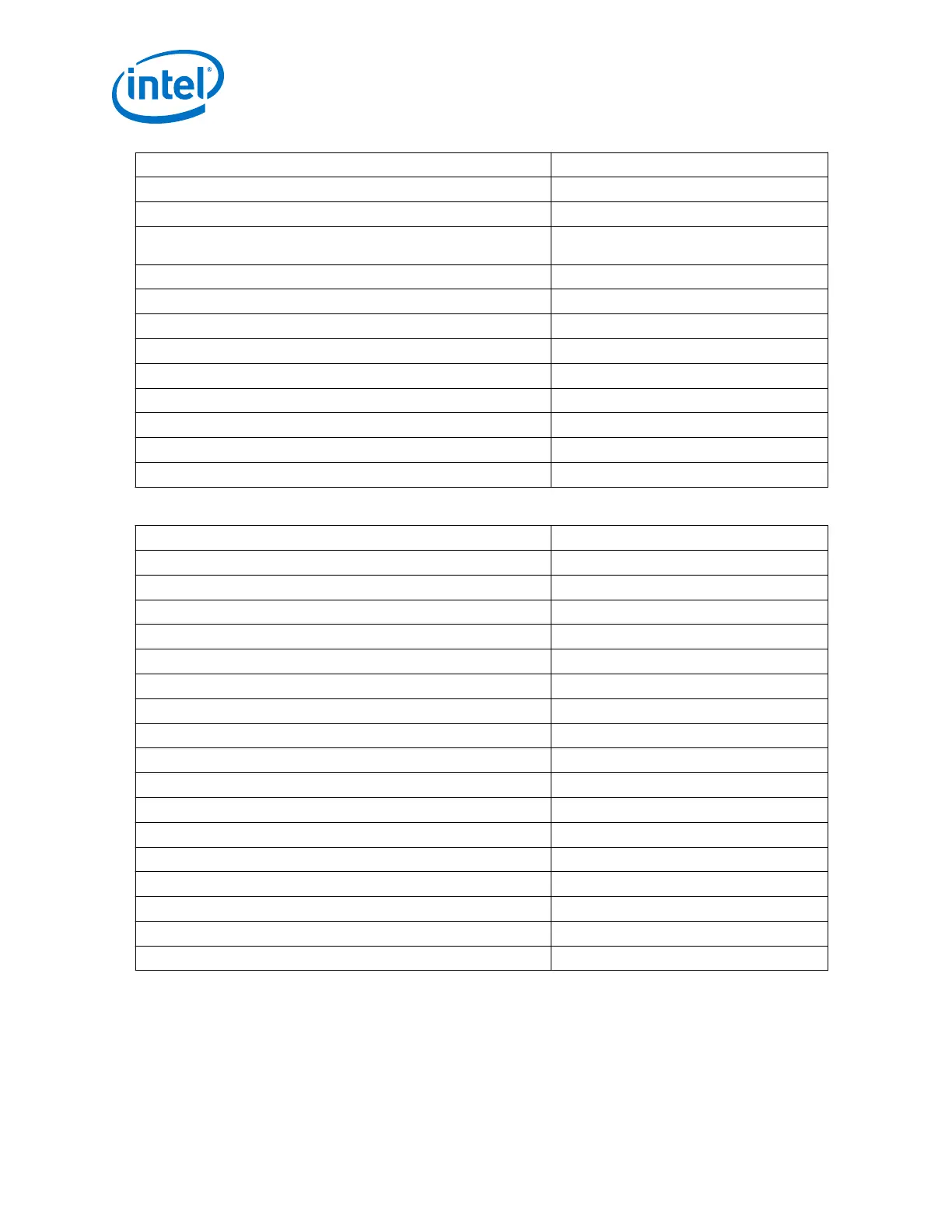

Parameter Range

TX local clock division factor 1, 2, 4, 8

Number of TX PLL clock inputs per channel 1, 2, 3, 4

Initial TX PLL clock input selection 0 (Depends on the Number of TX PLL clock

inputs per channel value)

Enable tx_pma_clkout port On/Off

Enable tx_pma_div_clkout port On/Off

tx_pma_div_clkout division factor Disabled, 1, 2, 33, 40, 66

Enable tx_pma_elecidle port On/Off

Enable tx_pma_qpipullup port (QPI) On/Off

Enable tx_pma_qpipulldn port (QPI) On/Off

Enable tx_pma_txdetectrx port (QPI) On/Off

Enable tx_pma_rxfound port (QPI) On/Off

Enable rx_seriallpbken port On/Off

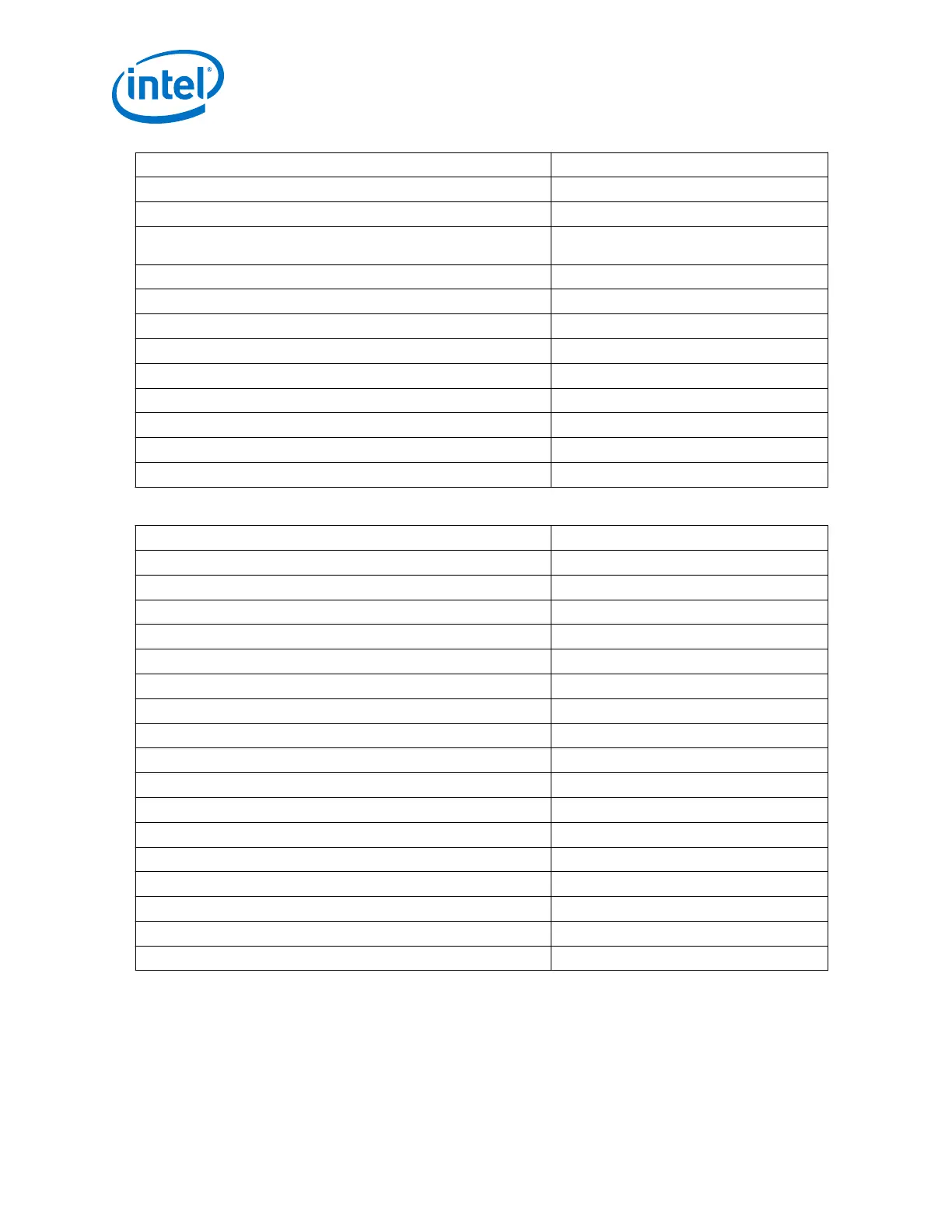

Table 219. RX PMA Parameters

Parameter Range

Number of CDR reference clocks 1, 2, 3, 4, 5

Selected CDR reference clock 0, 1, 2, 3, 4

Selected CDR reference clock frequency Legal range defined by Quartus Prime software

PPM detector threshold 100, 300, 500, 1000

CTLE adaptation mode manual

DFE adaptation mode disabled

Number of fixed dfe taps 3, 7

Enable rx_pma_clkout port On/Off

Enable rx_pma_div_clkout port On/Off

rx_pma_div_clkout division factor Disabled, 1, 2, 33, 40, 50, 66

Enable rx_pma_clkslip port On/Off

Enable rx_pma_qpipulldn port (QPI) On/Off

Enable rx_is_lockedtodata port On/Off

Enable rx_is_lockedtoref port On/Off

Enable rx_set_locktodata and rx_set_locktoref ports On/Off

Enable rx_seriallpbken port On/Off

Enable PRBS verifier control and status ports On/Off

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

316

Loading...

Loading...