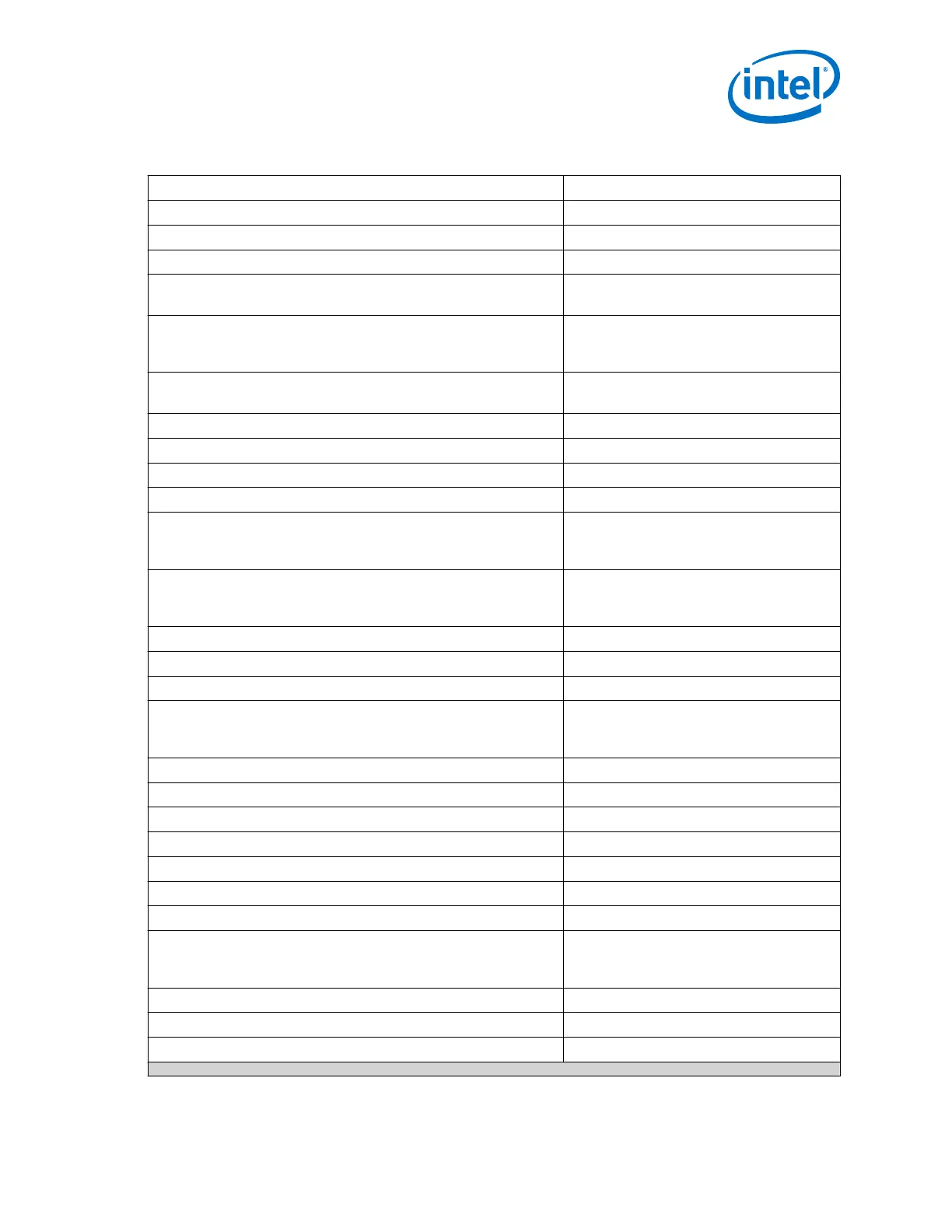

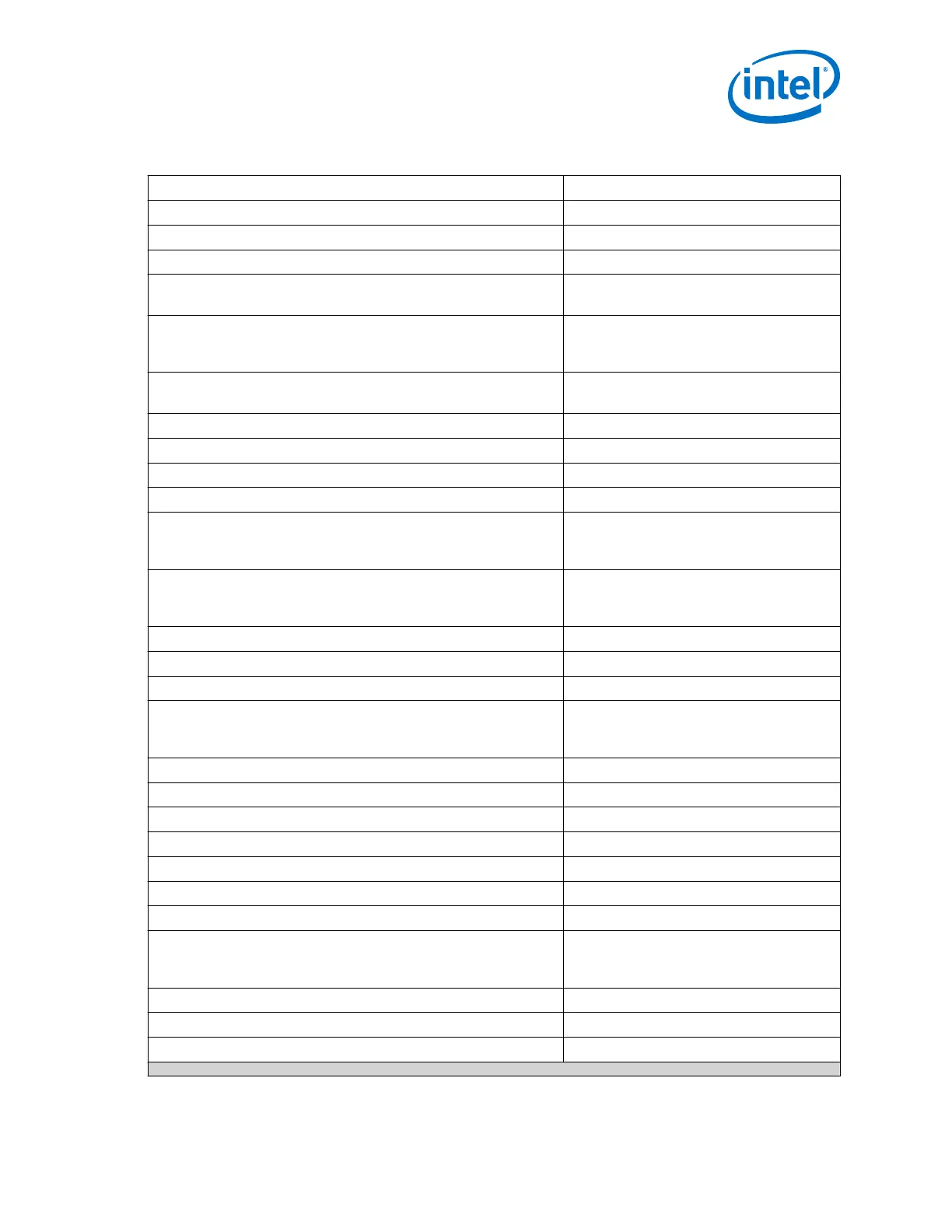

Table 220. Standard PCS Parameters

Parameter Range

Standard PCS / PMA interface width 8, 10, 16, 20

FPGA fabric / Standard TX PCS interface width 8, 10, 16, 20, 32, 40

FPGA fabric / Standard RX PCS interface width 8, 10, 16, 20, 32, 40

Enable 'Standard PCS' low latency mode

On/Off

Off (for Basic with Rate Match)

TX FIFO mode

low_latency

register_fifo

fast_register

RX FIFO Mode

low_latency

register_fifo

Enable tx_std_pcfifo_full port On/Off

Enable tx_std_pcfifo_empty port On/Off

Enable rx_std_pcfifo_full port On/Off

Enable rx_std_pcfifo_empty port On/Off

TX byte serializer mode

Disabled

Serialize x2

Serialize x4

RX byte deserializer mode

Disabled

Deserialize x2

Deserialize x4

Enable TX 8B/10B encoder On/Off

Enable TX 8B/10B disparity control On/Off

Enable RX 8B/10B decoder On/Off

RX rate match FIFO mode

Disabled

Basic 10-bit PMA (for Basic with Rate Match)

Basic 20-bit PMA (for Basic with Rate Match)

RX rate match insert/delete -ve pattern (hex) User-defined value

RX rate match insert/delete +ve pattern (hex) User-defined value

Enable rx_std_rmfifo_full port On/Off

Enable rx_std_rmfifo_empty port On/Off

PCI Express* Gen 3 rate match FIFO mode Bypass

Enable TX bit slip On/Off

Enable tx_std_bitslipboundarysel port On/Off

RX word aligner mode

bitslip

manual (PLD controlled)

synchronous state machine

RX word aligner pattern length 7, 8, 10, 16, 20, 32, 40

RX word aligner pattern (hex) User-defined value

Number of word alignment patterns to achieve sync 0-255

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

317

Loading...

Loading...