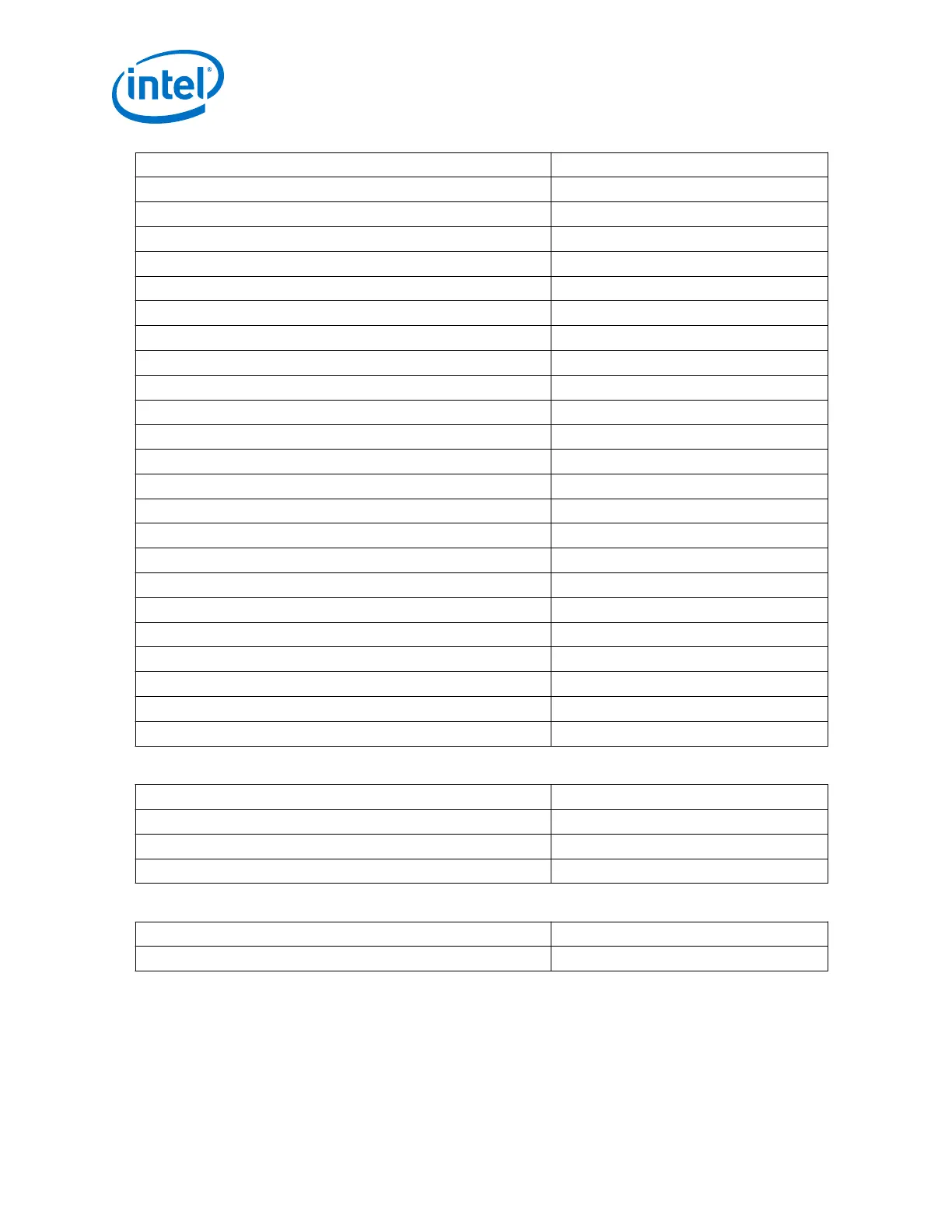

Parameter Range

Number of invalid data words to lose sync 0-63

Number of valid data words to decrement error count 0-255

Enable fast sync status reporting for deterministic latency SM On/Off

Enable rx_std_wa_patternalign port On/Off

Enable rx_std_wa_a1a2size port On/Off

Enable rx_std_bitslipboundarysel port On/Off

Enable rx_bitslip port On/Off

Enable TX bit reversal On/Off

Enable TX byte reversal On/Off

Enable TX polarity inversion On/Off

Enable tx_polinv port On/Off

Enable RX bit reversal On/Off

Enable rx_std_bitrev_ena port On/Off

Enable RX byte reversal On/Off

Enable rx_std_byterev_ena port On/Off

Enable RX polarity inversion On/Off

Enable rx_polinv port On/Off

Enable rx_std_signaldetect port On/Off

Enable PCIe dynamic datarate switch ports Off

Enable PCIe pipe_hclk_in and pipe_hclk_out ports Off

Enable PCIe Gen 3 analog control ports Off

Enable PCIe electrical idle control and status ports Off

Enable PCIe pipe_rx_polarity port Off

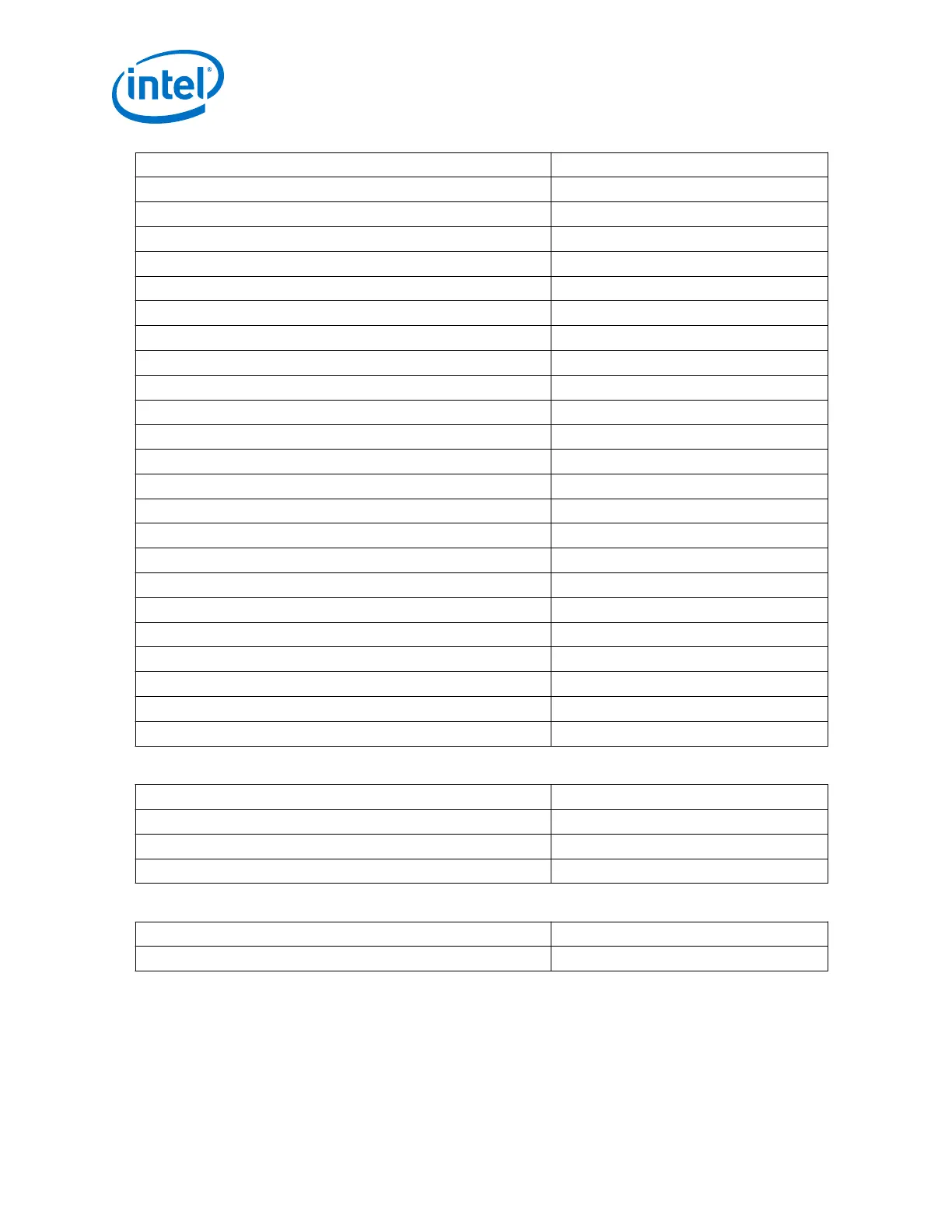

Table 221. Dynamic Reconfiguration Parameters

Parameter Range

Enable dynamic reconfiguration On/Off

Share reconfiguration interface On/Off

Enable Altera Debug Master Endpoint On/Off

Table 222. Generation Options Parameters

Parameter Range

Generate parameter documentation file On/Off

Related Information

Using the Arria 10 Transceiver Native PHY IP Core on page 45

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

318

Loading...

Loading...