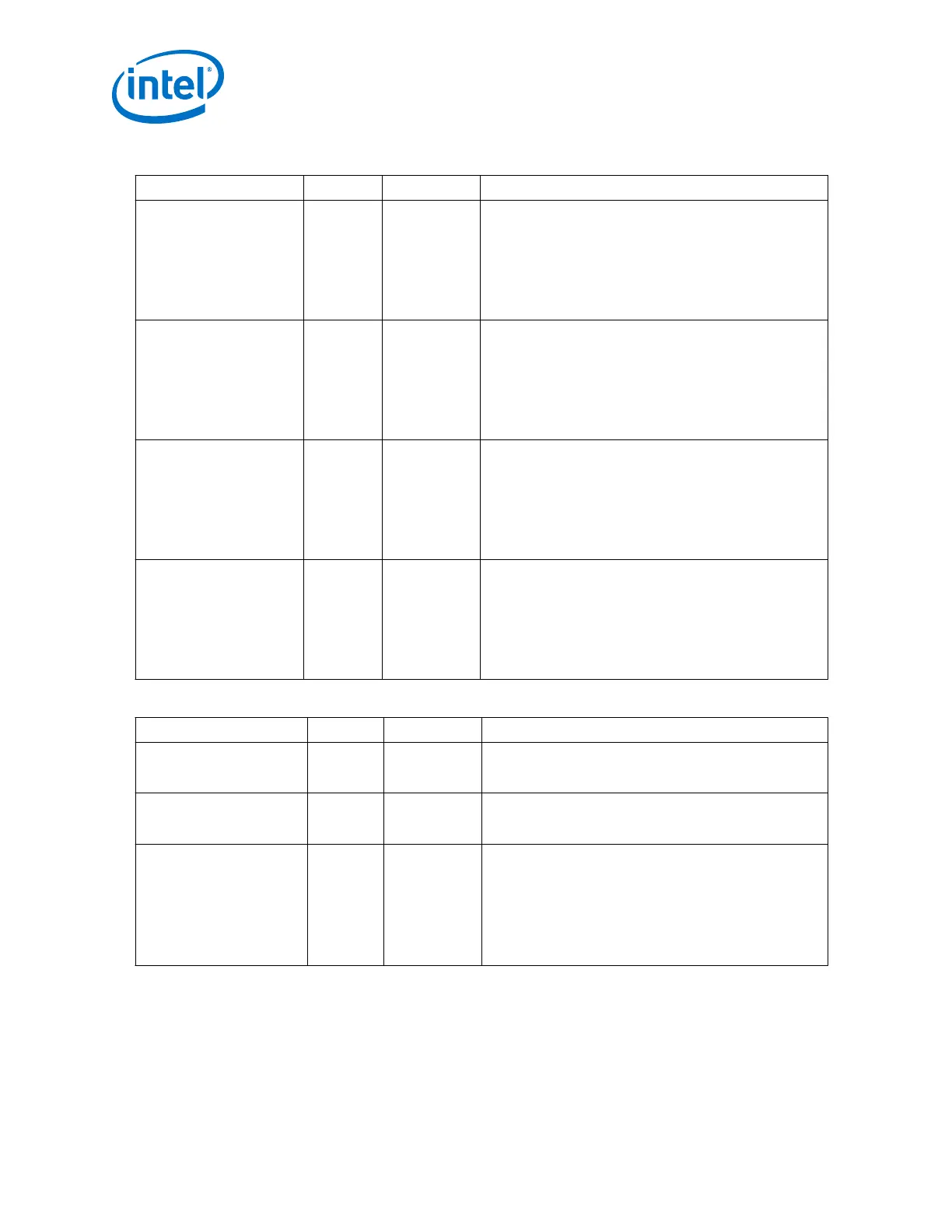

Table 70. Standard PCS FIFO

Name Direction Clock Domain Description

tx_std_pcfifo_full[<n

>-1:0]

Output Synchronous

to the clock

driving the

write side of

the FIFO

(tx_coreclki

n or

tx_clkout)

Indicates when the standard TX FIFO is full.

tx_std_pcfifo_empty[<

n>-1:0]

Output Synchronous

to the clock

driving the

write side of

the FIFO

(tx_coreclki

n or

tx_clkout)

Indicates when the standard TX FIFO is empty.

rx_std_pcfifo_full[<n

>-1:0]

Output Synchronous

to the clock

driving the

read side of

the FIFO

(rx_coreclki

n or

rx_clkout)

Indicates when the standard RX FIFO is full.

rx_std_pcfifo_empty[<

n>-1:0]

Output Synchronous

to the clock

driving the

read side of

the FIFO

(rx_coreclki

n or

rx_clkout)

Indicates when the standard RX FIFO is empty.

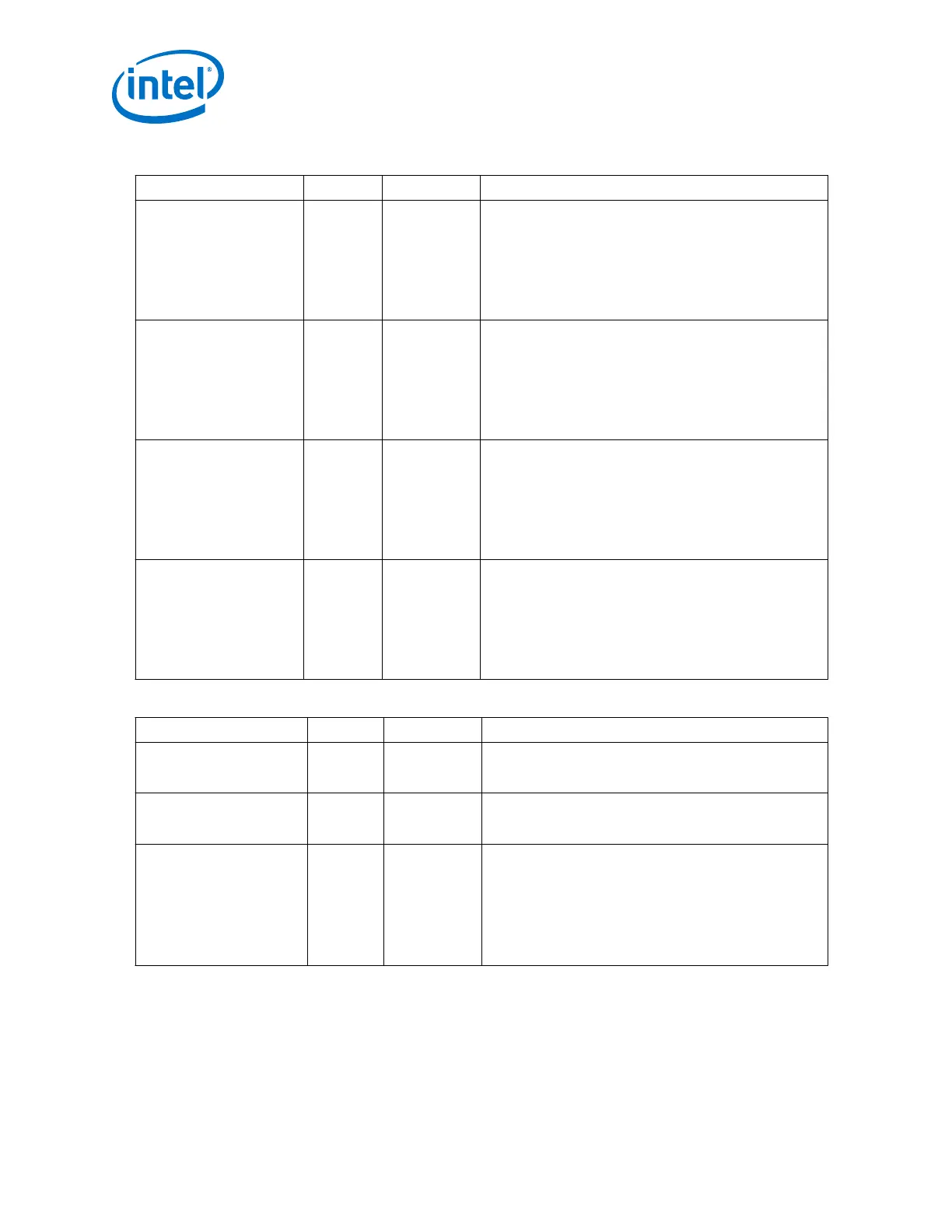

Table 71. Rate Match FIFO

Name Direction Clock Domain Description

rx_std_rmfifo_full[<n

>-1:0]

Output Asynchronous Rate match FIFO full flag. When asserted the rate match

FIFO is full. You must synchronize this signal. This port is

only used for GigE mode.

rx_std_rmfifo_empty[<

n>-1:0]

Output Asynchronous Rate match FIFO empty flag. When asserted, match FIFO is

empty. You must synchronize this signal. This port is only

used for GigE mode.

rx_rmfifostatus[<n>-1

:0]

Output Asynchronous Indicates FIFO status. The following encodings are defined:

• 2'b00: Normal operation

•

2'b01: Deletion, rx_std_rmfifo_full = 1

•

2'b10: Insertion, rx_std_rmfifo_empty = 1

•

2'b11: Full. rx_rmfifostatus is a part of

rx_parallel_data. rx_rmfifostatus corresponds

to rx_parallel_data[14:13].

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

88

Loading...

Loading...