RL78/F13, F14 CHAPTER 15 SERIAL ARRAY UNIT

R01UH0368EJ0210 Rev.2.10 980

Dec 10, 2015

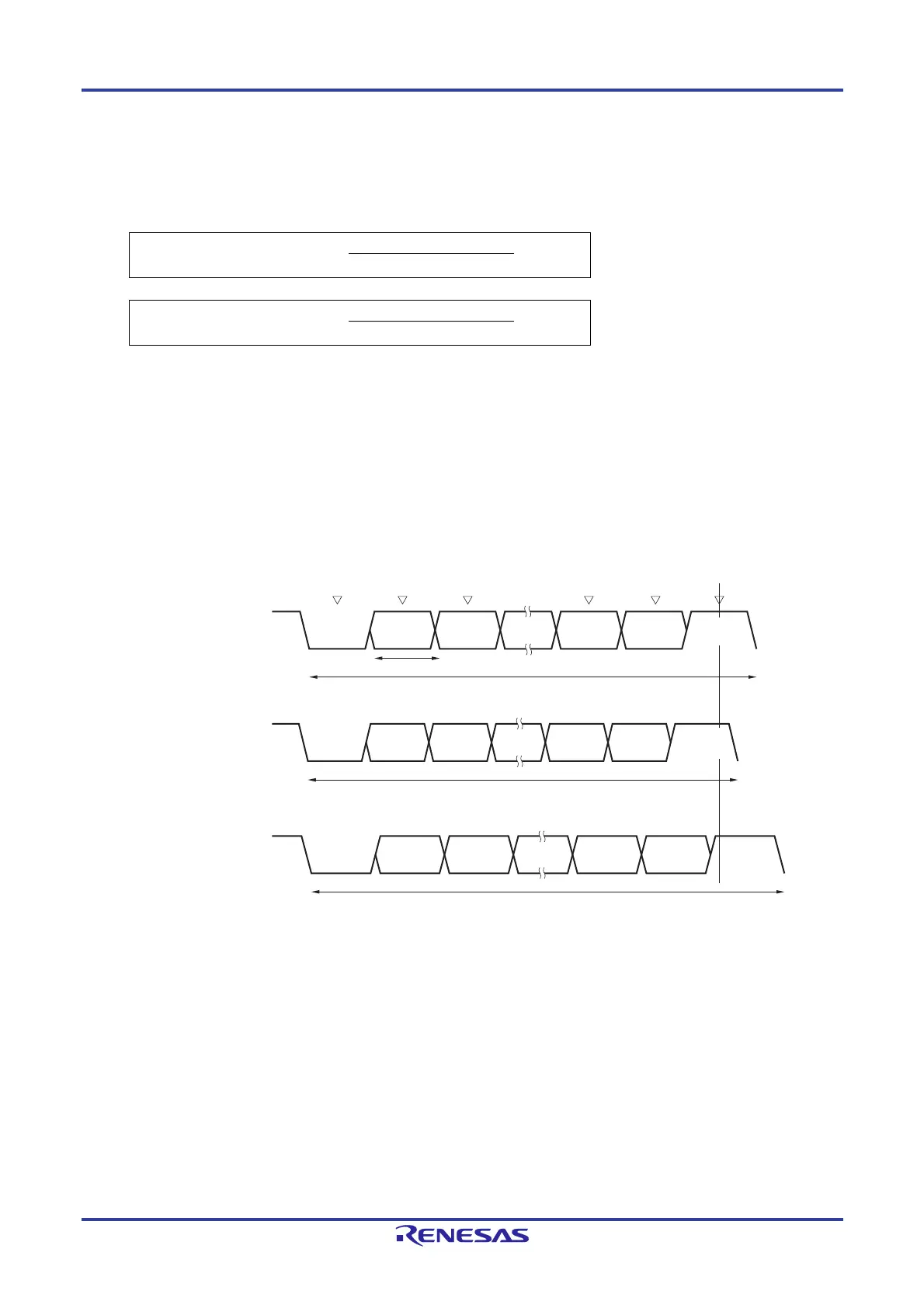

(3) Permissible baud rate range for reception

The permissible baud rate range for reception during UART (UART0, UART1) communication can be calculated by

the following expression. Make sure that the baud rate at the transmission side is within the permissible baud rate

range at the reception side.

(Maximum receivable baud rate) =

2 × k × Nfr

× Brate

2 × k × Nfr − k + 2

(Minimum receivable baud rate) =

2 × k × (Nfr − 1)

× Brate

2 × k × Nfr − k − 2

Brate: Calculated baud rate value at the reception side (See 15.7.3 (1) Baud rate calculation expression.)

k: SDRmn[15:9] + 1

Nfr: 1 data frame length [bits]

= (Start bit) + (Data length) + (Parity bit) + (Stop bit)

Remark m: Unit number (m = 0, 1), n: Channel number (n = 1), mn = 01, 11

Figure 15-135. Permissible Baud Rate Range for Reception (1 Data Frame Length = 11 Bits)

As shown in Figure 15-135, the timing of latching receive data is determined by the division ratio set by bits 15 to 9

of serial data register mn (SDRmn) after the start bit is detected. If the last data (stop bit) is received before this latch

timing, the data can be correctly received.

FL

1 data frame (11 × FL)

(11 × FL)

min.

(11 × FL) max.

Data frame length

of SAU

Start

bit

Bit 0 Bit 1 Bit 7

Parity

bit

Permissible minimum

data frame length

Permissible maximum

data frame length

Stop

bit

Start

bit

Bit 0 Bit 1 Bit 7

Parity

bit

Latch

timing

Stop

bit

Start

bit

Bit 0 Bit 1 Bit 7

Parity

bit

Stop

bit

Loading...

Loading...