RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1421

Dec 10, 2015

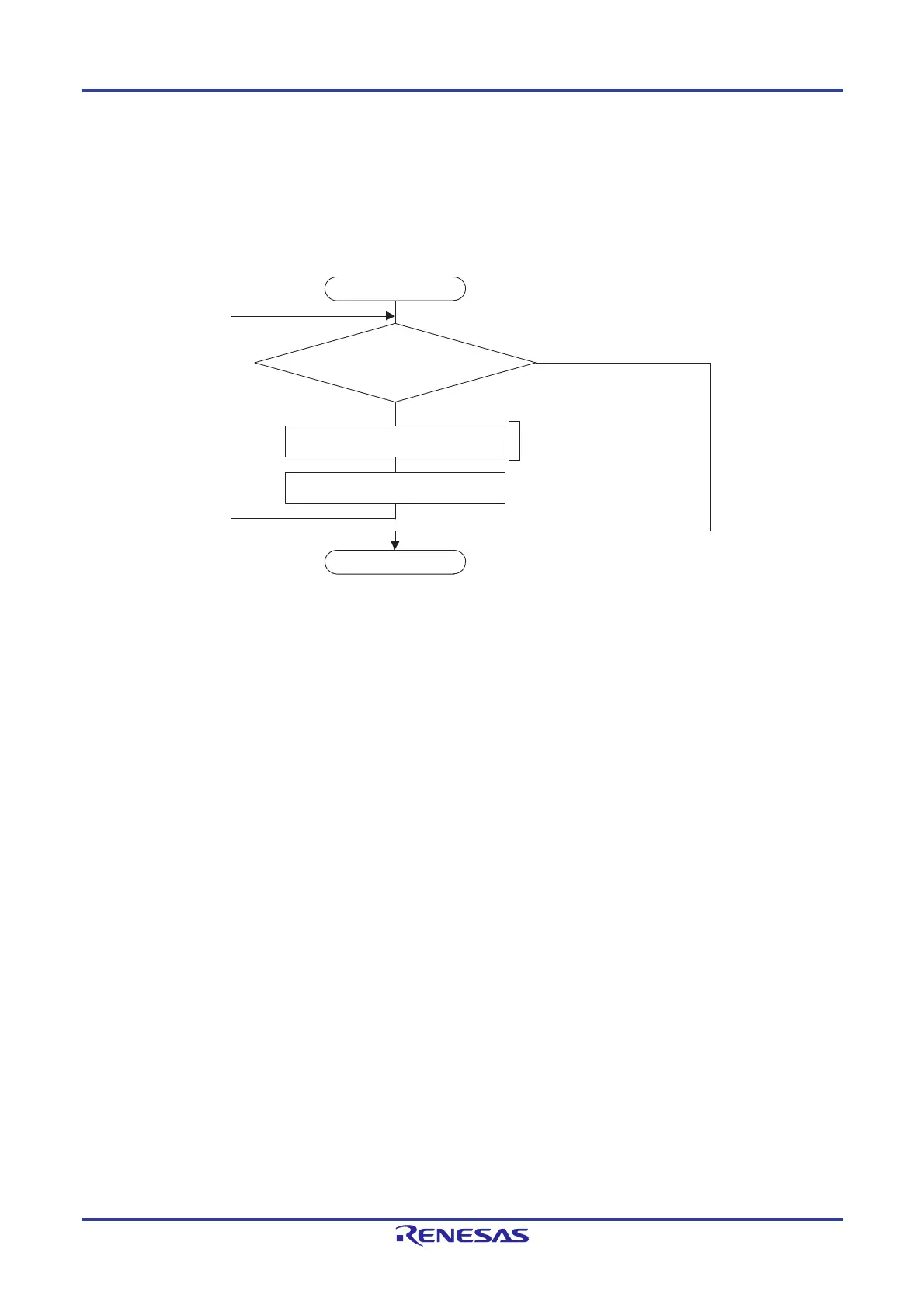

18.12.3 Transmit History Buffer Reading Procedure

Transmit history data can be read from the THLACCi register. The next data can be accessed by writing H'FF to the

corresponding THLPCTRi register after reading a set of data. Figure 18-32 shows the transmit history buffer reading

procedure.

Figure 18-32. Transmit History Buffer Reading Procedure

No

Read transmit history data

from the THLACCi register.

Set the THLPCTRi register to H'FF.

Read data when the RPAGE bit in

the GRWCR register is set to 1.

Yes

Remark i = 0

Start

End

Is transmit history buffer empty?

(Is the THLEMP bit in the THLSTSi register 1?)

Loading...

Loading...