RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1375

Dec 10, 2015

18.3.78 CAN Global RAM Window Control Register (GRWCR)

Address GRWCRL: F038AH, GRWCRH: F038BH

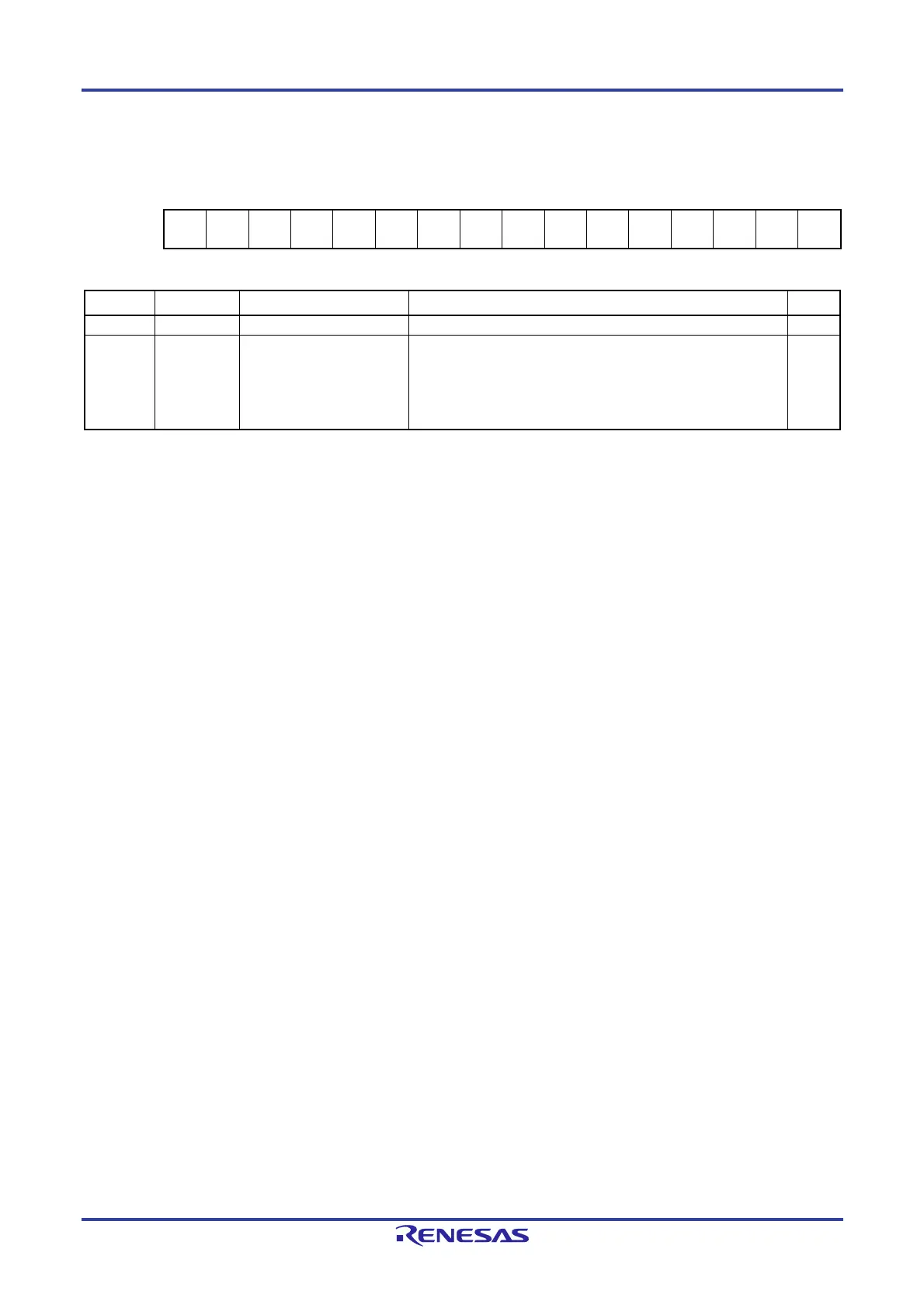

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

— — — — — — — — — — — — — — — RPA

GE

After Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

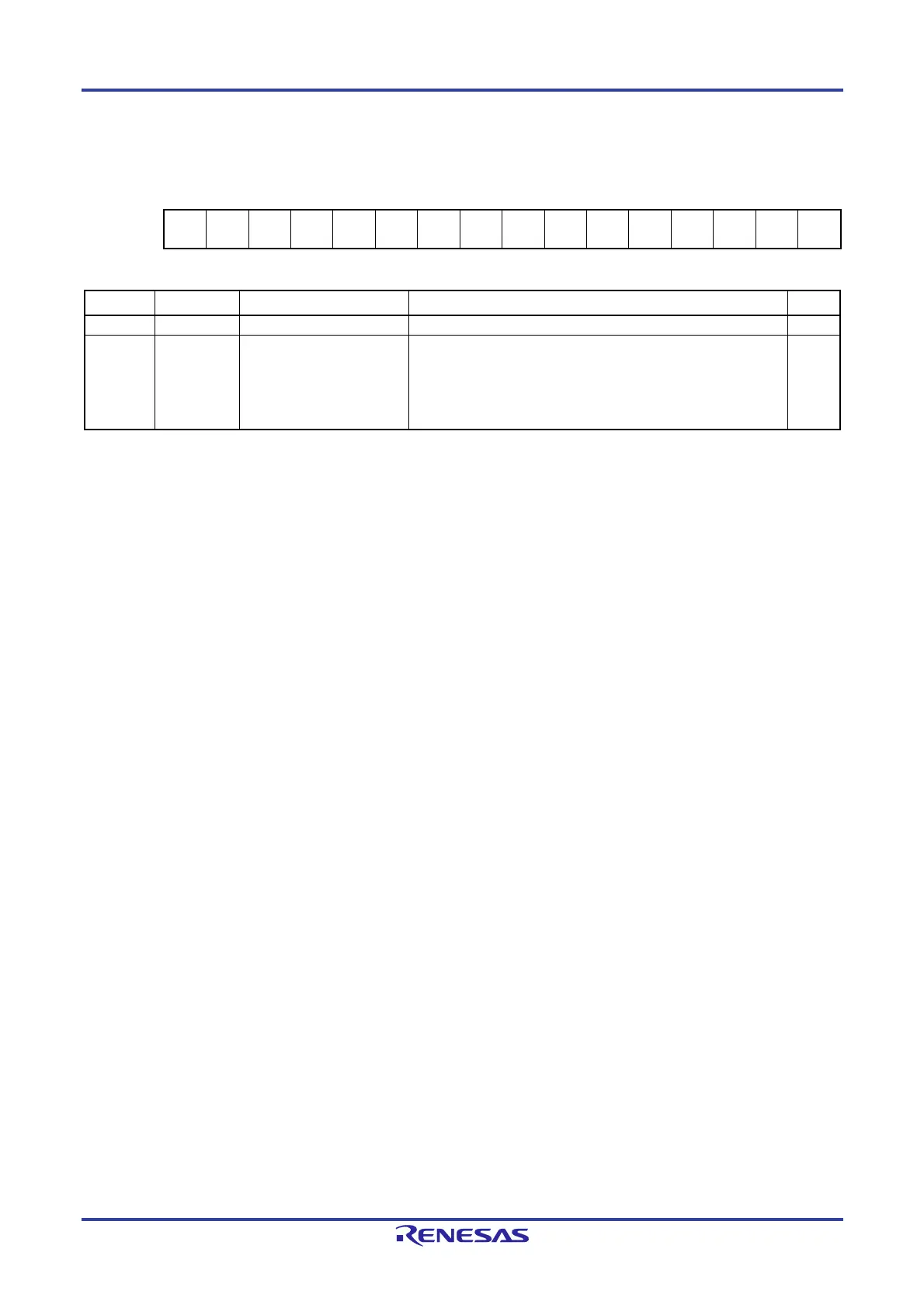

Bit Symbol Bit Name Description R/W

15 to 1 — Reserved The write value should always be 0. R

0 RPAGE RAM Window Select 0: Selects window 0 (receive rule entry registers, CAN RAM test

registers)

1: Selects window 1 (receive buffer, receive FIFO buffer,

transmit/receive FIFO buffer, transmit buffer, transmit history

data access register)

R/W

• RPAGE Bit

This bit is used to select a window for the switching of registers that are allocated to addresses from H’F03A0 to

H’F0681.

[Registers allocated when the RPAGE bit is set to 0 (window 0 selected)]

• CAN receive rule entry registers: GAFLIDLj, GAFLIDHj, GAFLMLj, GAFLMHj, GAFLPLj, GAFLPHj

• CAN RAM test registers: RPGACCr

[Registers allocated when the RPAGE bit is set to 1 (window 1 selected)]

• CAN receive buffer registers: RMIDLn, RMIDHn, RMTSn, RMPTRn, RMDF0n to RMDF3n

• CAN receive FIFO access registers: RFIDLm, RFIDHm, RFTSm, RFPTRm, RFDF0m to RFDF3m

• CANi transmit/receive FIFO access registers: CFIDLk, CFIDHk, CFTSk, CFPTRk, CFDF0k to CFDF3k

• CANi transmit buffer registers: TMIDLp, TMIDHp, TMPTRp, TMDF0p to TMDF3p

• CANi transmit history buffer access register: THLACCi

Loading...

Loading...