RL78/F13, F14 CHAPTER 9 REAL-TIME CLOCK

R01UH0368EJ0210 Rev.2.10 663

Dec 10, 2015

9.3.5 RTC clock select register (RTCCL)

The RTCCL register is used to select the operation clock of the real-time clock.

Set the RTCCL register by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

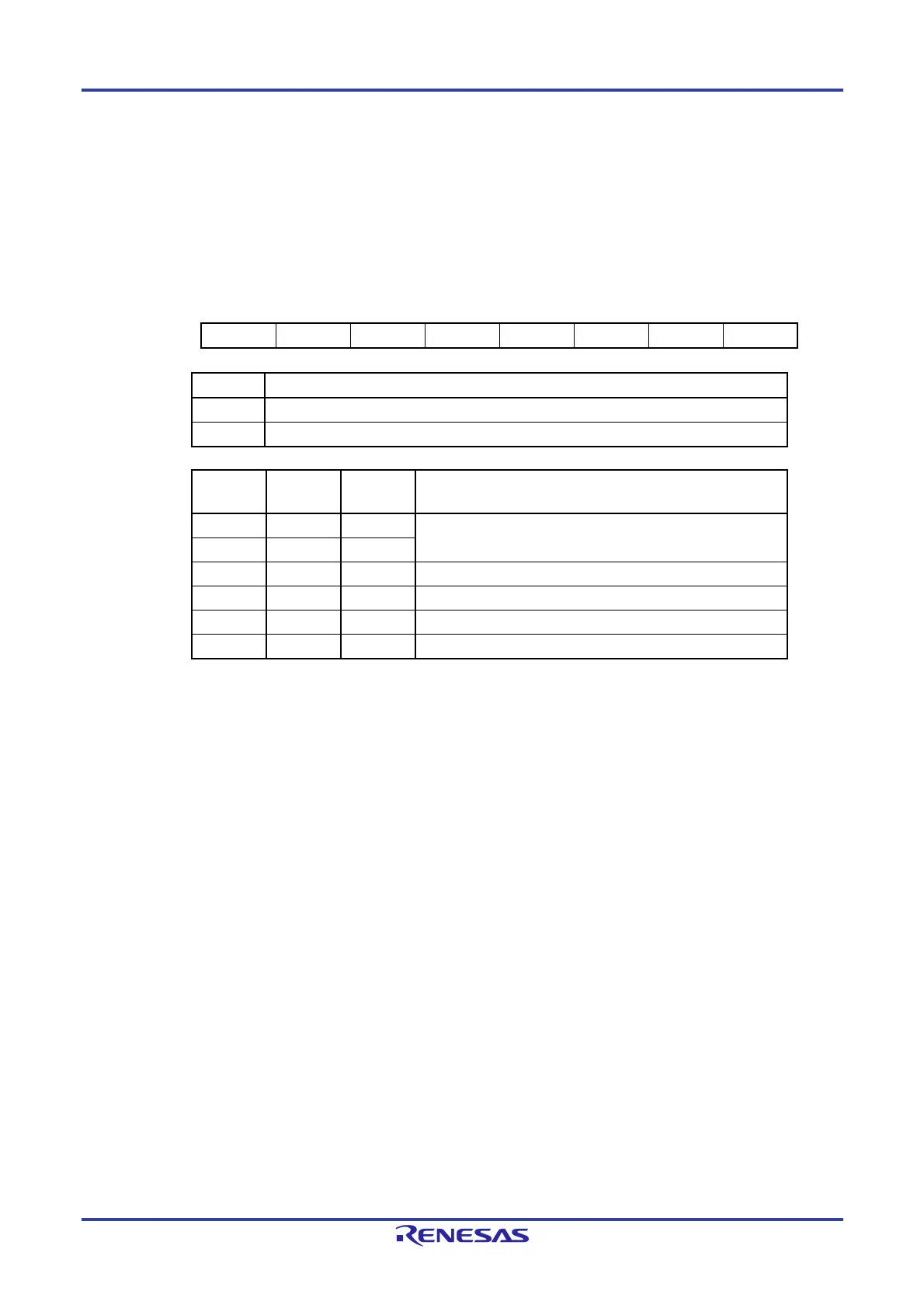

Figure 9-6. Format of RTC clock select register (RTCCL)

Address: F02C8H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

RTCCL RTCCL_7 RTCCL_6 - - - - RTCCKS1 RTCCKS0

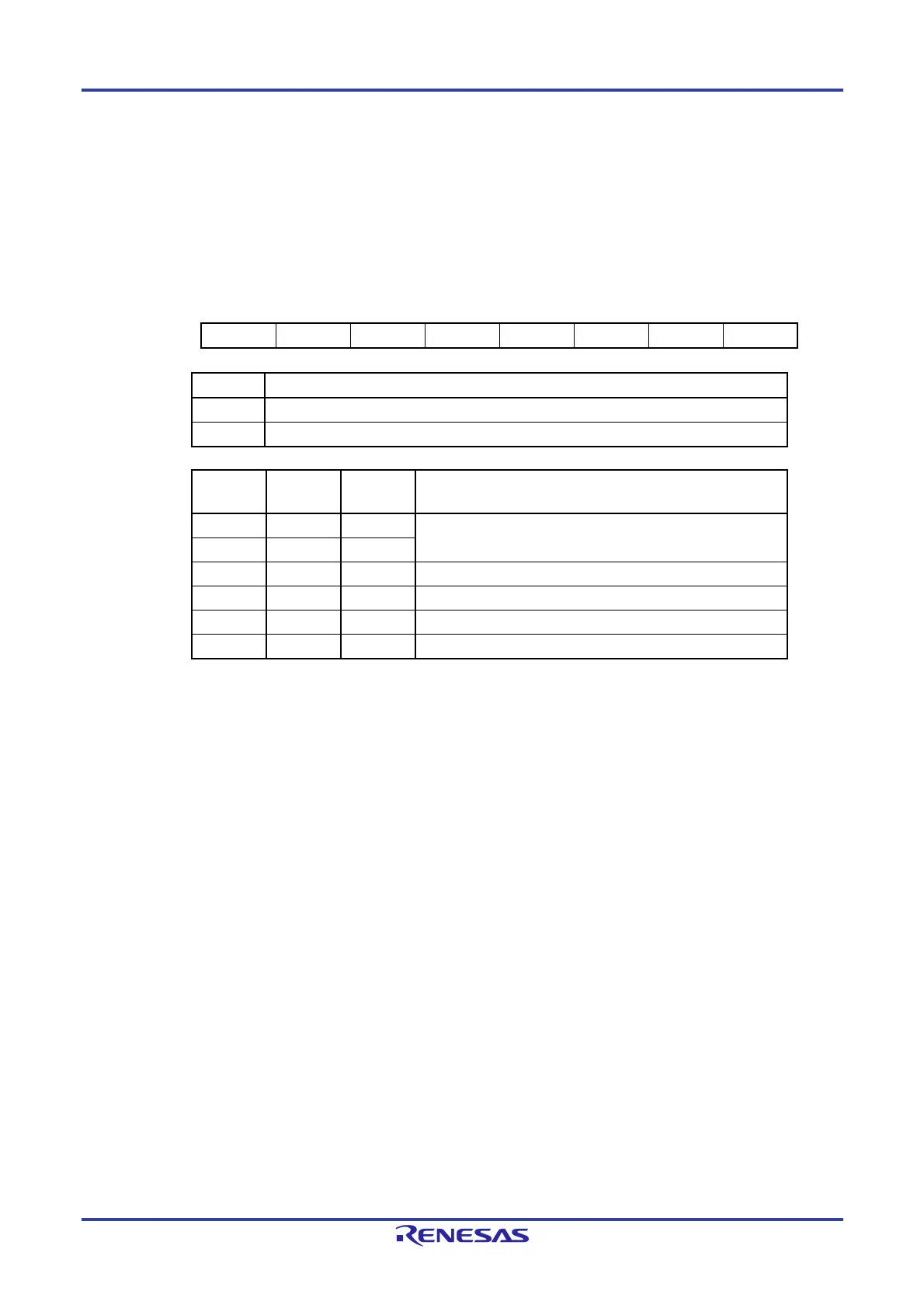

RTCCL_7 Control over operation of the low-speed on-chip oscillator

0 High-speed system clock (fMX)

1 High-speed on-chip oscillator clock (fIH)

RTCCKS1

Note 3

RTCCKS0 RTCCL_6 Control of RTC operating clock selection

0 0

Subsystem clock (fSUB)

Note 1

0 1

1 0 0 fMX or fIH / 128

Note 2

1 0 1 fMX or fIH / 122

Note 2

1 1 0 fMX or fIH / 256

Note 2

1 1 1 fMX or fIH / 244

Note 2

Notes 1. When the SELLOSC bit in the CKSEL register is 1, the subsystem clock (f

SUB) cannot be

supplied to the input clock (fRTC) of the real time clock.

2. Switch after selecting RTCCL_7.

3. When setting the RTCCKS1 bit to 1, first set the CSS bit in the CKC register to 0 to select the

main system/PLL select clock (f

MP) as the CPU/peripheral hardware clock (fCLK).

Cautions 1. 20, 30, or 32-pin products do not have a subsystem clock (f

SUB), so it should not be

selected.

2. Set bits 2 to 5 to 0.

Remark : don’t care

Loading...

Loading...