RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1360

Dec 10, 2015

18.3.63 CANi Transmit Buffer Transmit Request Status Register (TMTRSTS) (i = 0)

Address TMTRSTSL: F0374H, TMTRSTSH: F0375H

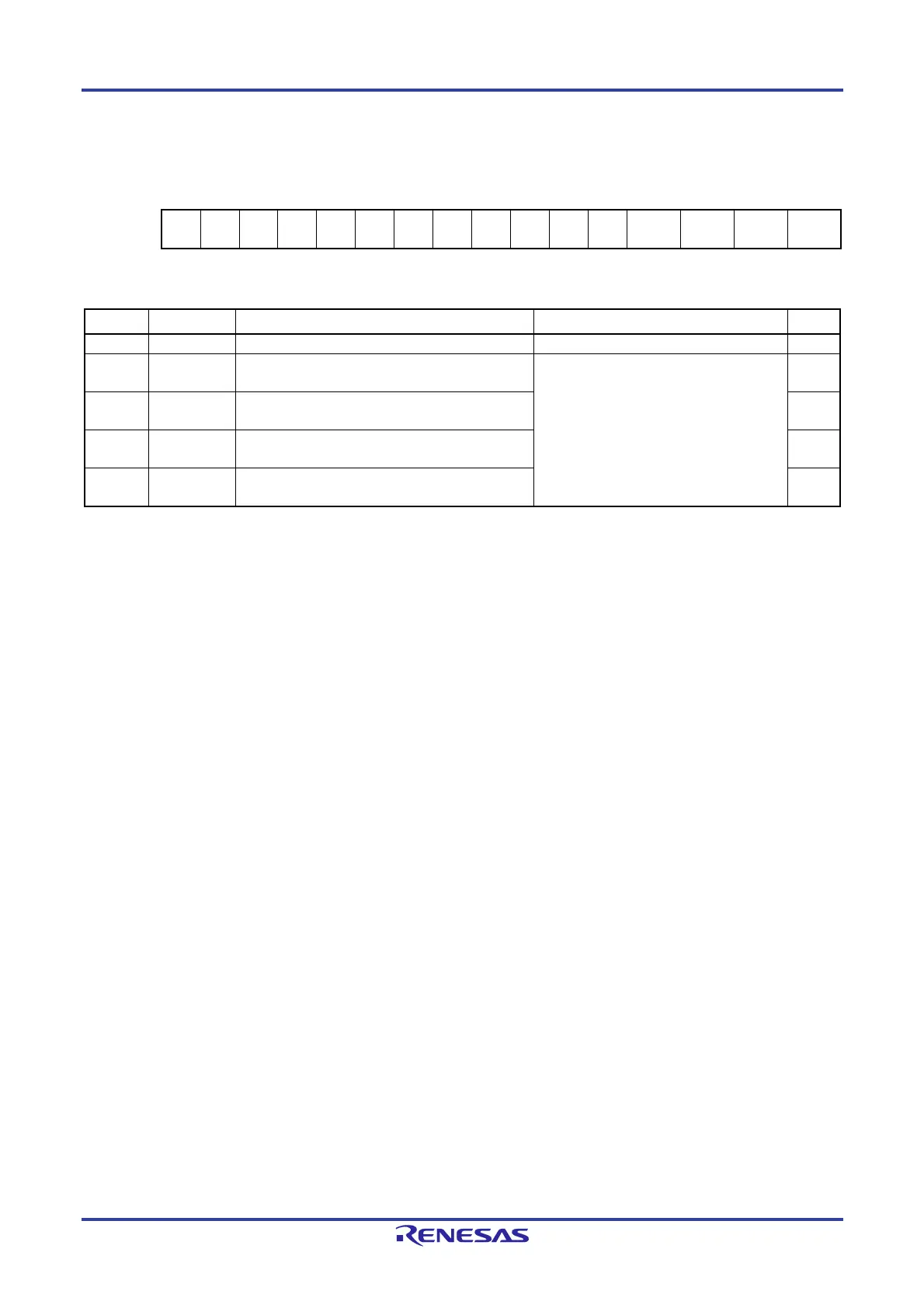

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

— — — — — — — — — — — — TMTR

STS3

TMTR

STS2

TMTR

STS1

TMTR

STS0

After

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

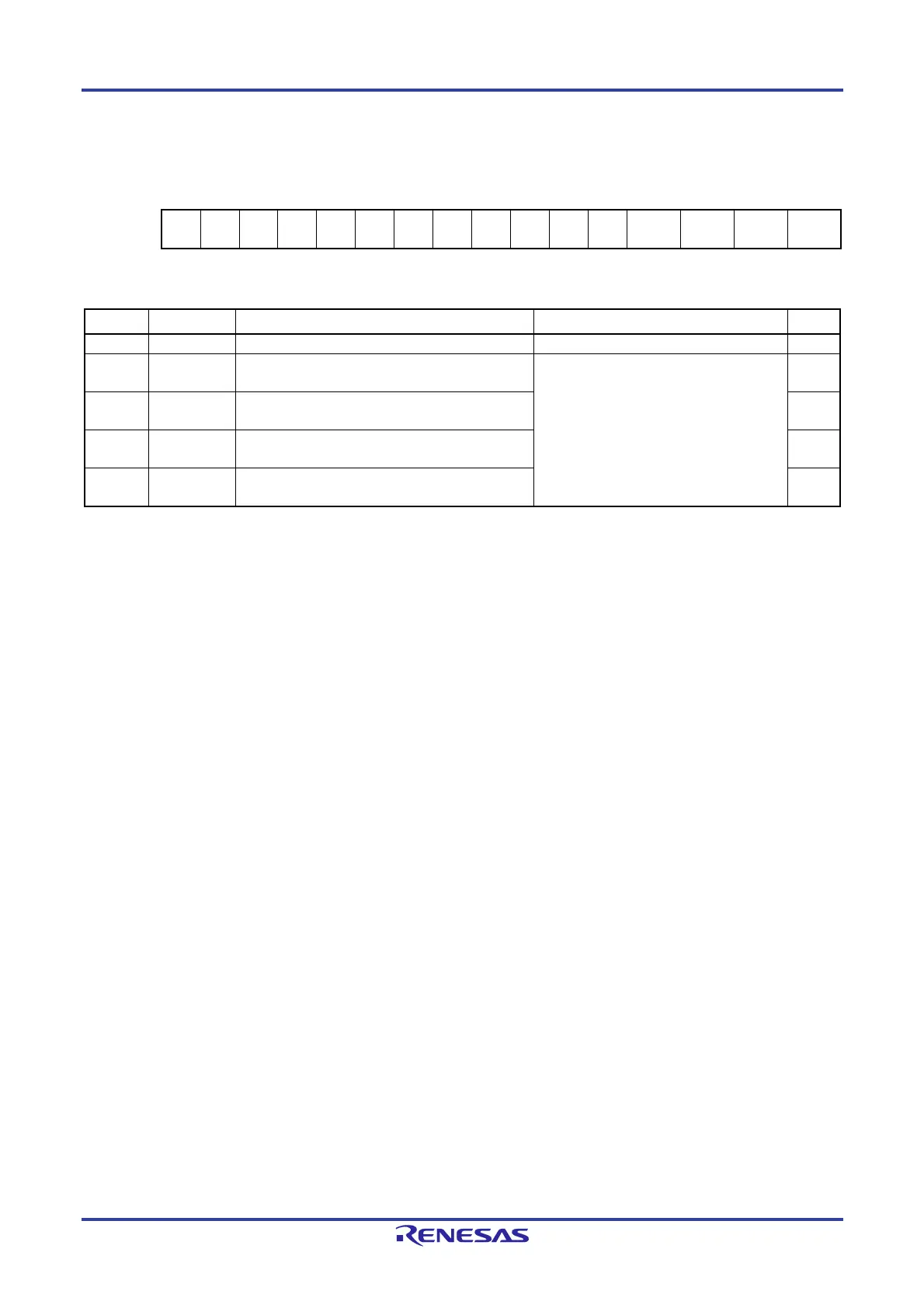

Bit Symbol Bit Name Description R/W

15 to 4 — Reserved These bits are always read as 0. R

3 TMTRSTS3 CANi Transmit Buffer 3 Transmit Request Status

Flag

0: No transmit request is present.

1: A transmit request is present.

R

2 TMTRSTS2 CANi Transmit Buffer 2 Transmit Request Status

Flag

R

1 TMTRSTS1 CANi Transmit Buffer 1 Transmit Request Status

Flag

R

0 TMTRSTS0 CANi Transmit Buffer 0 Transmit Request Status

Flag

R

• TMTRSTSp Flags (p = 0 to 3)

These flags indicate the status of the TMTR bit in the TMCp register.

When the TMTR bit is set to 1 (transmission is requested), the corresponding TMTRSTSp flag is set to 1.

The corresponding TMTRSTSp flag is cleared to 0 when the TMTR bit is set to 0 (transmission is not requested)

or in channel reset mode.

Loading...

Loading...