RL78/F13, F14 CHAPTER 5 CLOCK GENERATOR

R01UH0368EJ0210 Rev.2.10 408

Dec 10, 2015

5.6.5 Example of Setting Low-Speed On-Chip Oscillator

An example of setting the low-speed on-chip oscillator as the CPU clock is shown below.

<1> Select f

IL with the SELLOSC bit of the CKSEL register.

Set the SELLOSC bit to 1 to set fSL for the low-speed on-chip oscillator.

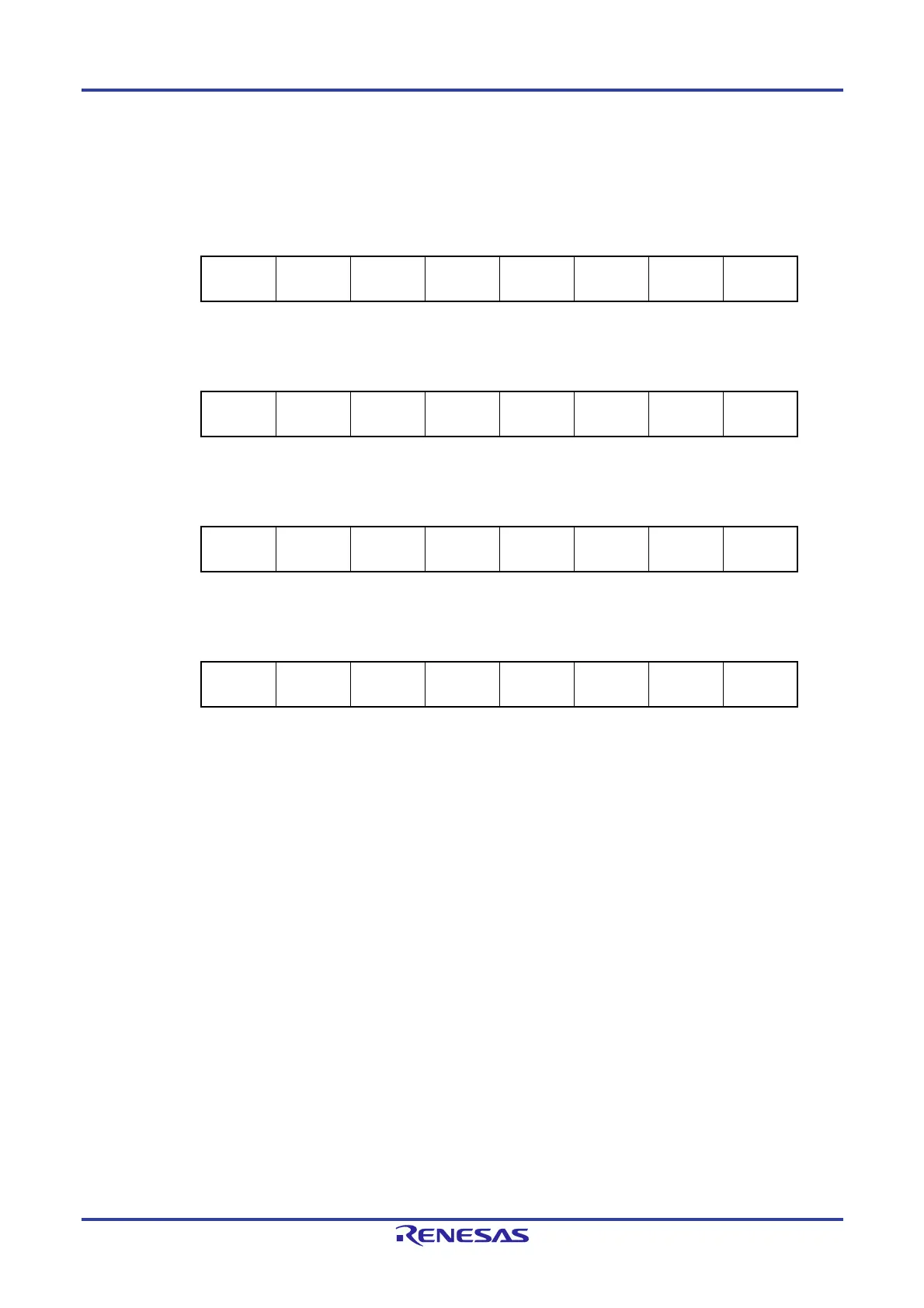

7 6 5 4 3 2 1 0

CKSEL

0

0

0

0

0

TRD_CKSEL

0

0

SELLOSC

1

<2> Select the operation mode of the subsystem clock with the OSCSELS bit of the CMC register.

Set the OSCSELS bit to 1 to select the input port mode (low-speed on-chip oscillator operation mode).

7 6 5 4 3 2 1 0

CMC

EXCLK

0

OSCSEL

0

EXCLKS

0

OSCSELS

1

0

AMPHS1

0/1

AMPHS0

0/1

AMPH

0

<3> Select the CPU/peripheral hardware clock with the CSS bit of the CKC register.

Set the CSS bit to 1 to specify CPU clock = f

SL (low-speed on-chip oscillator).

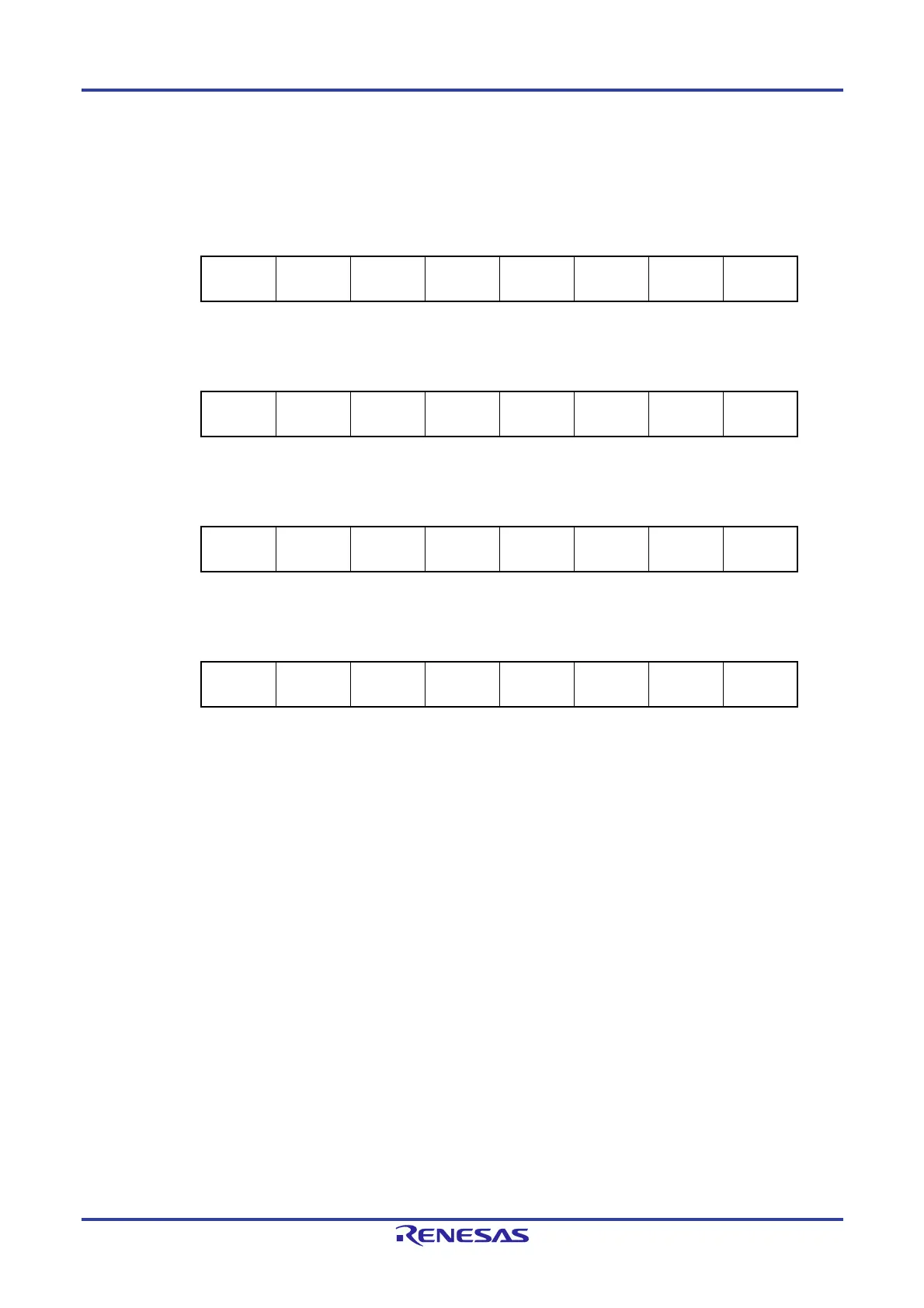

7 6 5 4 3 2 1 0

CKC

CLS

0

CSS

1

MCS

0

MCM0

1

0

0

0

0

<4> Confirm that f

SL (low-speed on-chip oscillator) is selected as the CPU/peripheral hardware clock (CLS = 1) with the

CLS bit of the CKC register.

7 6 5 4 3 2 1 0

CKC

CLS

1

CSS

1

MCS

0

MCM0

1

0

0

0

0

Loading...

Loading...