RL78/F13, F14 CHAPTER 21 INTERRUPT FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1474

Dec 10, 2015

21.2 Interrupt Sources and Configuration

Interrupt sources include maskable interrupts and software interrupts. In addition, they also have up to seven reset

sources (see Table 21-1). The vector codes that store the program start address when branching due to the generation of

a reset or various interrupt requests are two bytes each, so interrupts jump to a 64 K address of 00000H to 0FFFFH.

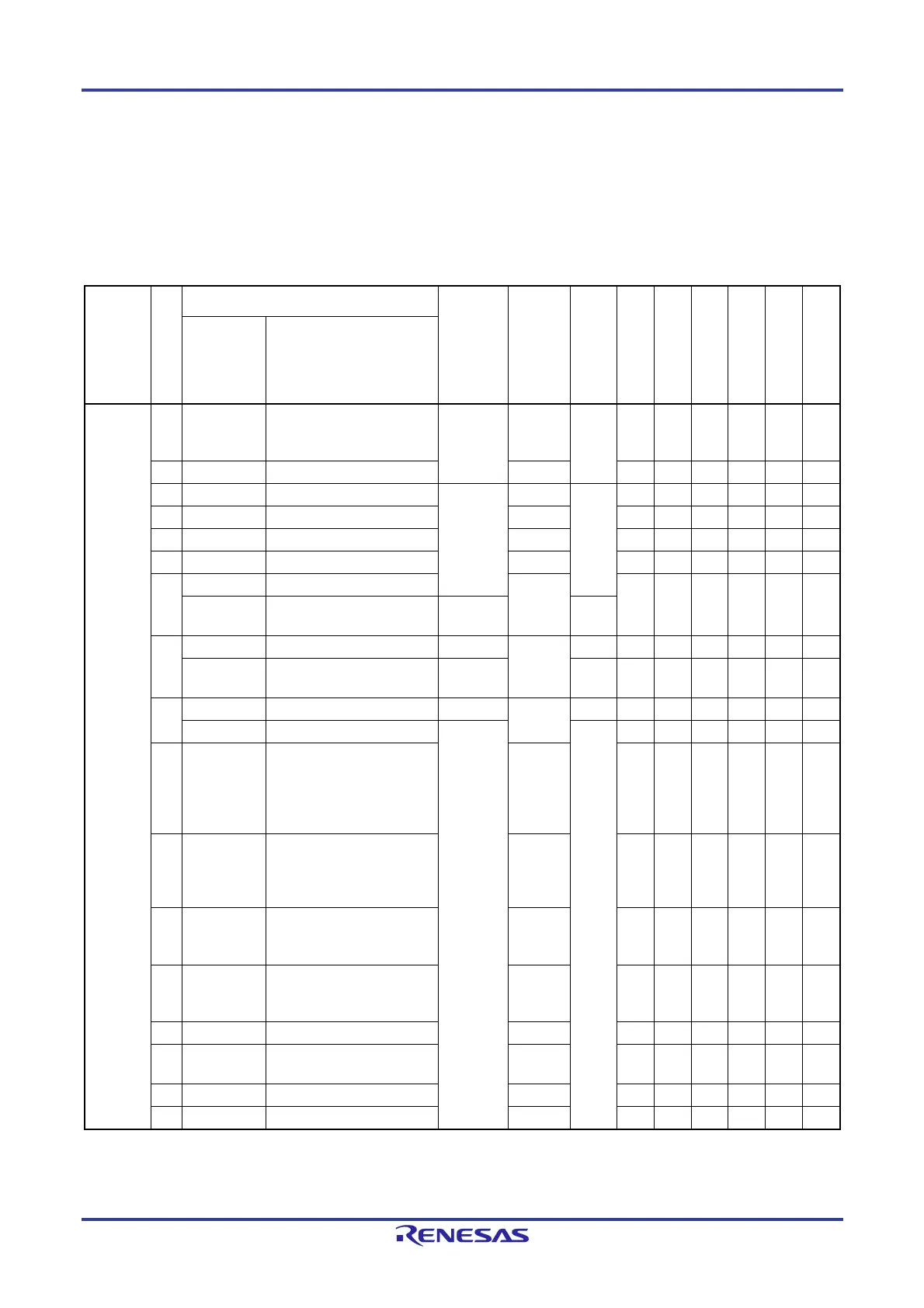

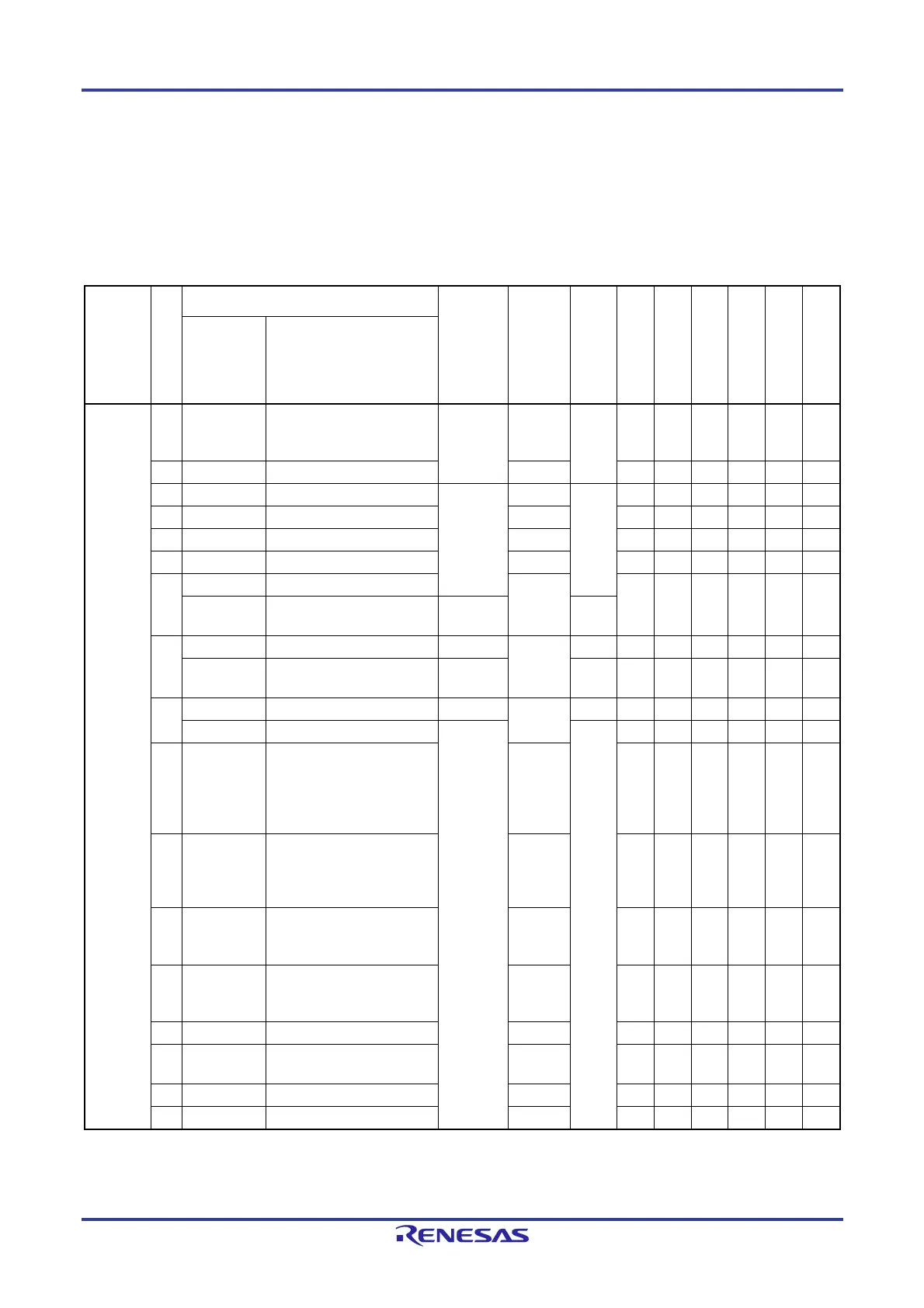

Table 21-1. Interrupt Source List (1/4)

Interrupt

Type

Default Priority

Note 1

Interrupt Source

Internal/

External

Vector

Table

Address

Basic Configuration

Type

Note 2

80, 100-pin

64-pin

48-pin

32-pin

30-pin

20-pin

Name Trigger

Maskable 0 INTWDTI Watchdog timer interval

Note 3

(75% of overflow

time+1/2f

WDT)

Internal 0004H (A)

1 INTLVI Voltage detection

Note 4

0006H

2 INTP0 Pin input edge detection 0 External 0008H (B)

3 INTP1 Pin input edge detection 1 000AH

4 INTP2 Pin input edge detection 2 000CH

5 INTP3 Pin input edge detection 3 000EH

6 INTP4

Note 7

Pin input edge detection 4 0010H

INTSPM

Note 7

Stack pointer

overflow/underflow

Internal (A)

7 INTP5

Note 8

Pin input edge detection 5 External 0012H (B)

INTCMP0

Note 8

Comparator detection 0 Internal (A)

Note 5

Note 5

Note 5

Note 5

Note 5

8 INTP13

Note 9

Pin input edge detection 13 External 0014H (B)

Note 6

INTCLM

Note 9

Main clock or PLL clock stop Internal (A)

9 INTST0/

INTCSI00/

INTIIC00

UART0 transmission transfer

end or buffer empty

interrupt/CSI00 transfer end

or buffer empty

interrupt

/IIC00 transfer end

0016H

10 INTSR0/

INTCSI01/

INTIIC01

UART0 reception transfer

end/CSI01 transfer end or

buffer empty interrupt

/IIC01

transfer end

0018H

11 INTTRD0 Timer RD0 input capture,

compare match, overflow,

underflow interrupt

001AH

12 INTTRD1 Timer RD1 input capture,

compare match, overflow,

underflow interrupt

001CH

13 INTTRJ0 Timer RJ0 001EH

14 INTRAM RAM 1-bit correction/2-bit error

detection

0020H

15 INTLIN0TRM LIN0 transmission

0022H

16 INTLIN0RVC LIN0 reception end 0024H

Loading...

Loading...