RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1377

Dec 10, 2015

18.3.80 CAN Global Test Control Register (GTSTCTRL)

Address GTSTCTRL: F038EH

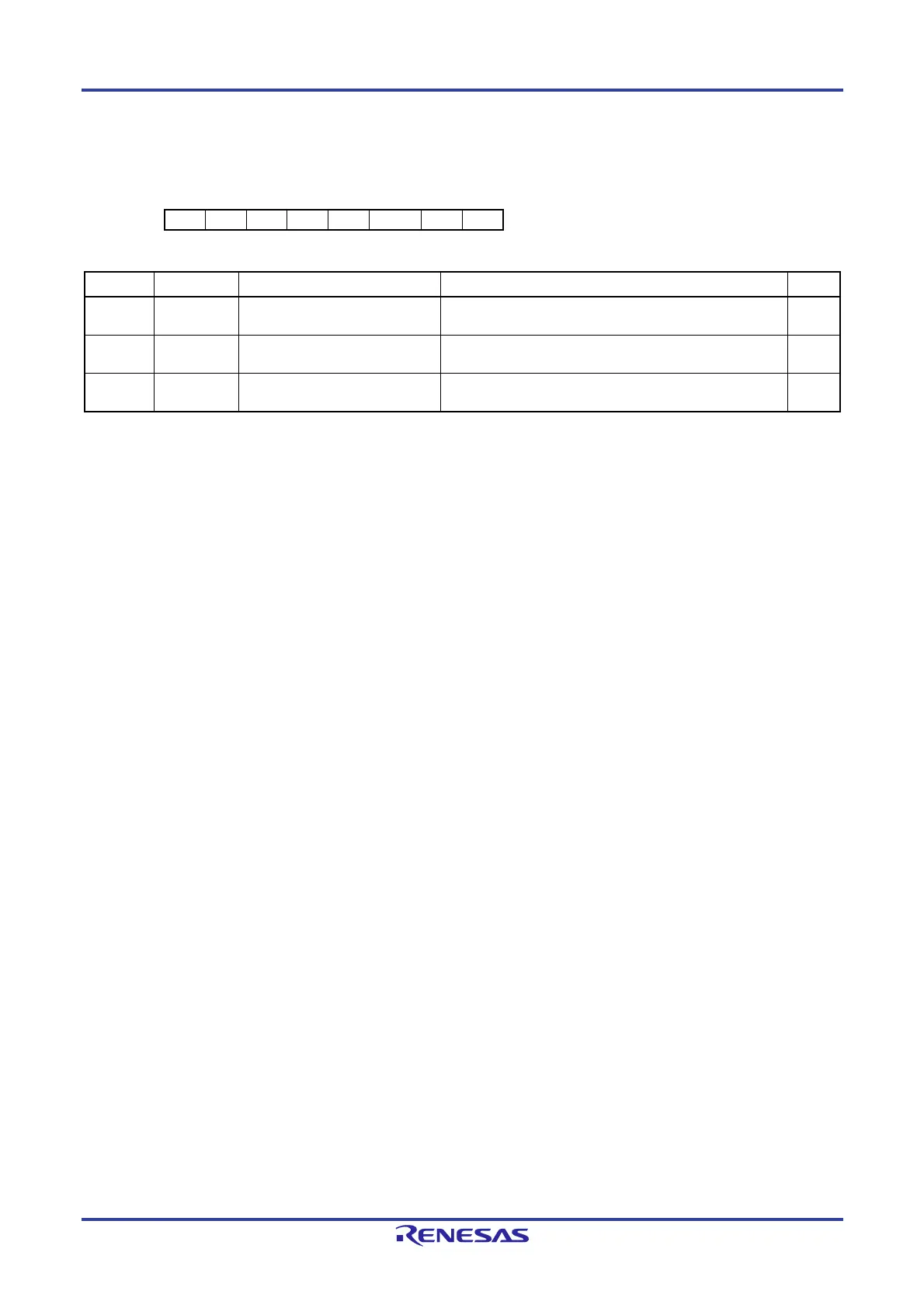

b7 b6 b5 b4 b3 b2 b1 b0

— — — — — RTME — —

After Reset 0 0 0 0 0 0 0 0

Bit Symbol Bit Name Description R/W

7 to 3 — Reserved These bits are always read as 0. The write value should

always be 0.

R

2 RTME RAM Test Enable 0: RAM test is disabled.

1: RAM test is enabled.

R/W

1, 0 — Reserved These bits are always read as 0. The write value should

always be 0.

R

• RTME Bit

Setting this bit to 1 enables RAM test. Modify this bit only in global test mode.

(1) Set the GMDC[1:0] bits in the GCTRL register to B'10 (global test mode).

(2) Release protection by successively writing H'7575 and H'8A8A to the GLOCKK register.

(3) Set the RTME bit to 1.

(4) Check that the RTME bit is set to 1.

Loading...

Loading...