RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1422

Dec 10, 2015

18.13 Test Settings

18.13.1 Self-Test Mode Setting Procedure

Self-test mode allows communication test on a channel basis by receiving messages transmitted from the own node.

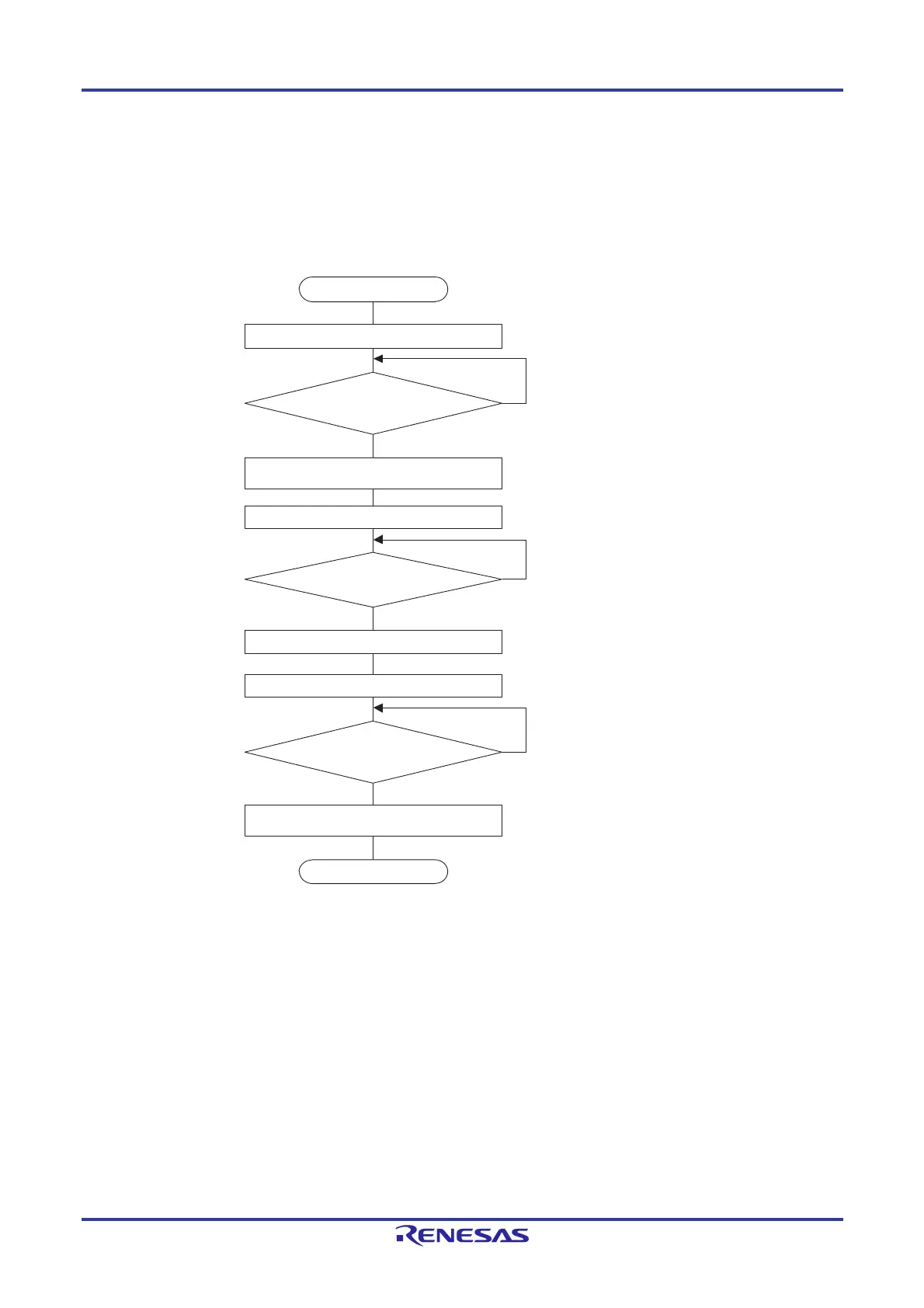

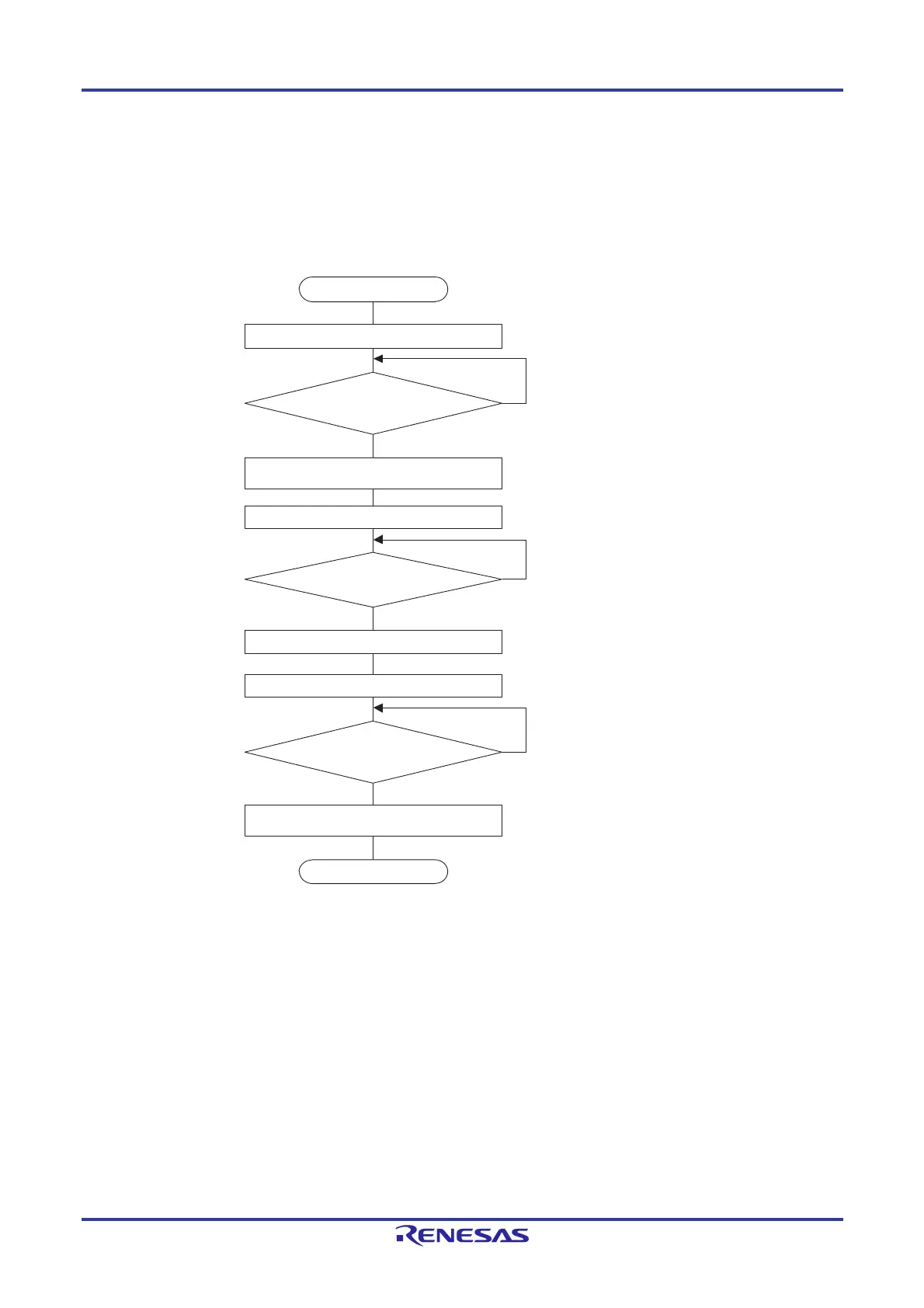

Figure 18-33 shows the self-test mode setting procedure.

Figure 18-33. Self-Test Mode Setting Procedure

No

No

No

Remark i = 0

Set the CHMDC[1:0] bits in the CiCTRL register to B'10.

Yes

Are all CSLPSTS, CHLTSTS, and

CRSTSTS flags in the CiSTSL register 0?

Yes

Yes

Perform self-test in channel i.

Set CTME bit in the CiCTRH register to 1.

Set the CTMS[1:0] bits to B'10 or B'11.

Communication test mode is enabled.

Self-test mode 0 (B'10) or 1 (B'11) is selected.

Channel halt mode

Start

Is CHLTSTS flag in the CiSTSL register 1

(in channel halt mode)?

Set the CHMDC[1:0] bits in the CiCTRL register to B'00.

Channel communication mode

Set the CHMDC[1:0] bits in the CiCTRL register to B'10.

Channel halt mode

Is CHLTSTS flag in the CiSTSL register 1

(in channel halt mode)?

Set CTME bit in the CiCTRH register to 0.

Set the CTMS[1:0] bits to B'00.

Communication test mode is disabled.

Standard test mode

End

Loading...

Loading...