RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1374

Dec 10, 2015

18.3.77 CANi Transmit History Buffer Pointer Control Register (THLPCTRi) (i = 0)

Address THLPCTR0L: F0384H, THLPCTR0H: F0385H

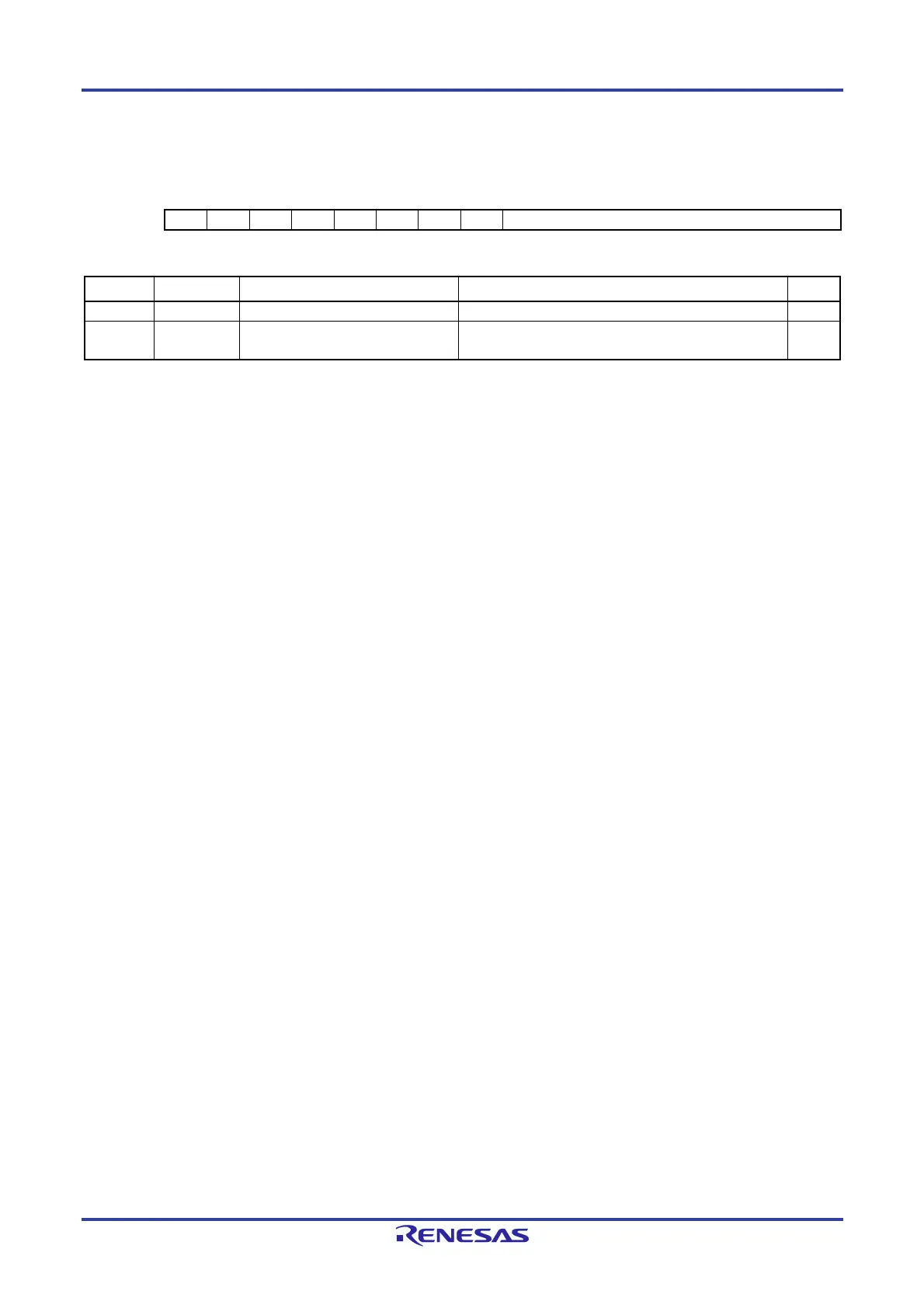

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

— — — — — — — — THLPC[7:0]

After Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

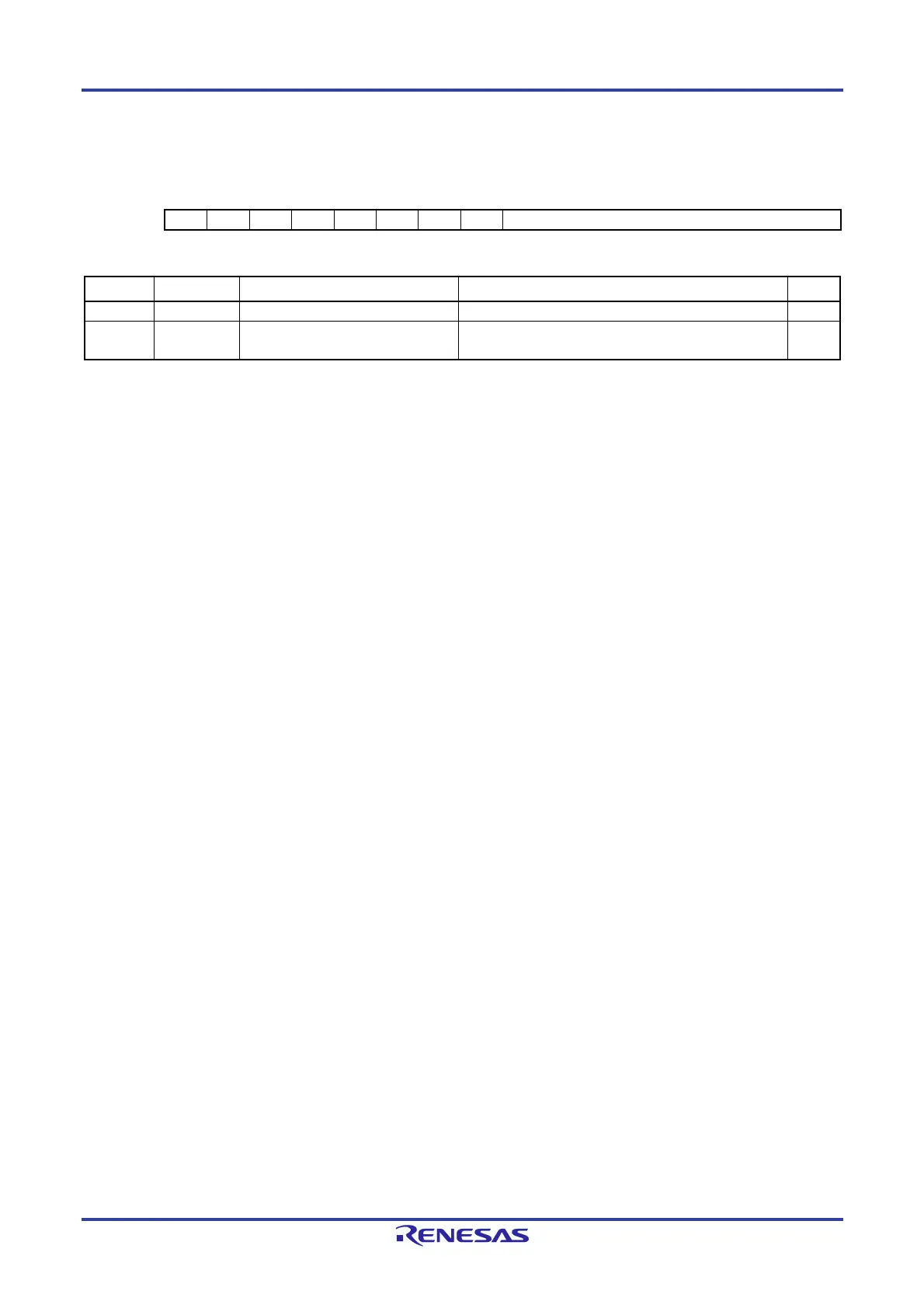

Bit Symbol Bit Name Description R/W

15 to 8 — Reserved The write value should always be 0. R

7 to 0 THLPC[7:0] Transmit History Buffer Pointer Writing H'FF to these bits moves the read pointer to the

next unread data in the transmit history buffer.

W

• THLPC [7:0] Bits

When the THLPC [7:0] bits are set to H'FF, the read pointer moves to the next data in the transmit history buffer.

At this time, the THLMC[3:0] (transmit history buffer unread data counter) value in the THLSTSi register is

decremented. After reading the THLACCi register, write H'FF to the THLPC [7:0] bits.

Write H'FF to the THLPC[7:0] bits when the THLE bit in the THLCCi register is set to 1 (transmit history buffer is

used) and the THLEMP flag in the THLSTSi register is 0.

Loading...

Loading...