RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1253

Dec 10, 2015

17.7.2 LIN Slave Mode

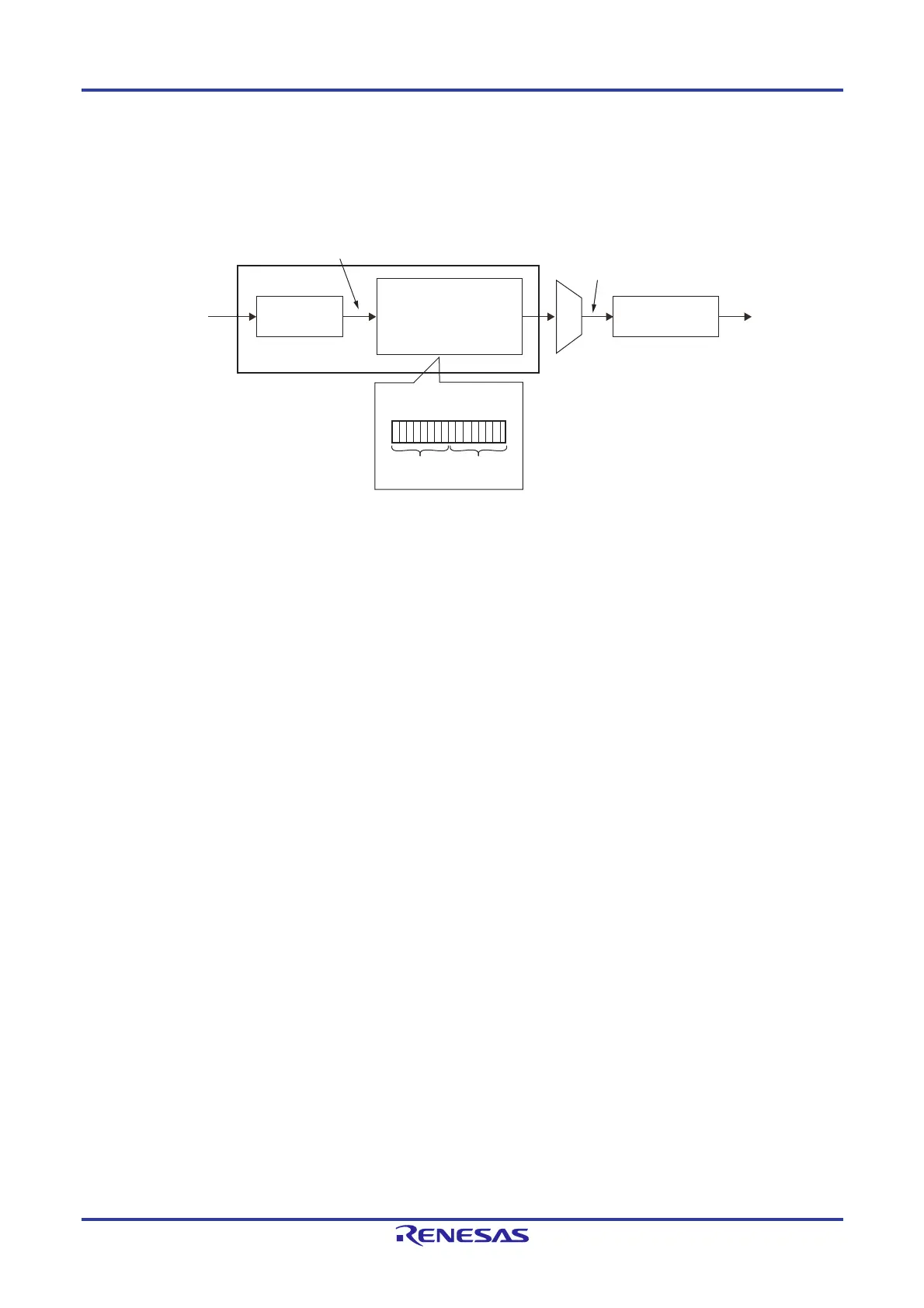

Figure 17-42 shows a block diagram of baud rate generation in LIN slave mode.

Figure 17-42. Block Diagram of Baud Rate Generation in LIN Slave Mode

Set the LIN communications clock source as follows.

LIN communications clock source = f

CLK

Note1

In the range from 4 MHz to 32 MHz

Note 1. When the timeout error detection is not used, the f

MX clock is selectable as the LIN communication clock source. In

that case, set at least 1.2 times the frequency of the LIN communication clock source to the CPU/peripheral

hardware clock(f

CLK).

In LIN slave mode [Auto Baud Rate], operation is possible with the baud rates from 1 kbps to 20 kbps. Set the prescaler

clock according to the target baud rate so that its frequency is the corresponding value from the list.

[Target baud rate] [Frequency of prescaler clock]

1 kbps to 20 kbps: 4 MHz

Note

1 kbps to less than 2.4 kbps: 4 MHz

2.4 kbps to 20 kbps: 8 MHz to 12 MHz

Note Set the NSPB[3:0] bits in the LWBRn register to 0011b (4 sampling).

Table 17-29 shows the examples of baud rate (19200, 10417, 9600, and 2400 bps) generation for each LIN communication

clock source frequency in LIN slave mode [fixed baud rate] and errors.

Note For the LIN communication clock source, refer to CHAPTER 5 CLOCK GENERATOR.

LIN communication

clock source

Note

Prescaler clock

Baud rate generator

Prescaler

(LPRS[2:0] bits)

16-bit counter

b15 b0

LBRPn1

register

LBRPn0

register

LIN baud rate prescaler

(LBRPn0 and LBRPn1

registers)

Bit sampling

1/4 or 1/8 or 1/16

(NSPB[3:0] bits)

Baud rate

fa

f

LIN

<R>

Loading...

Loading...