RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1364

Dec 10, 2015

18.3.67 CANi Transmit Buffer Register pAL (TMIDLp) (i = 0) (p = 0 to 3)

Address TMIDL0L: F0600H, TMIDL0H: F0601H TMIDL1L: F0610H, TMIDL1H: F0611H

TMIDL2L: F0620H, TMIDL2H: F0621H TMIDL3L: F0630H, TMIDL3H: F0631H

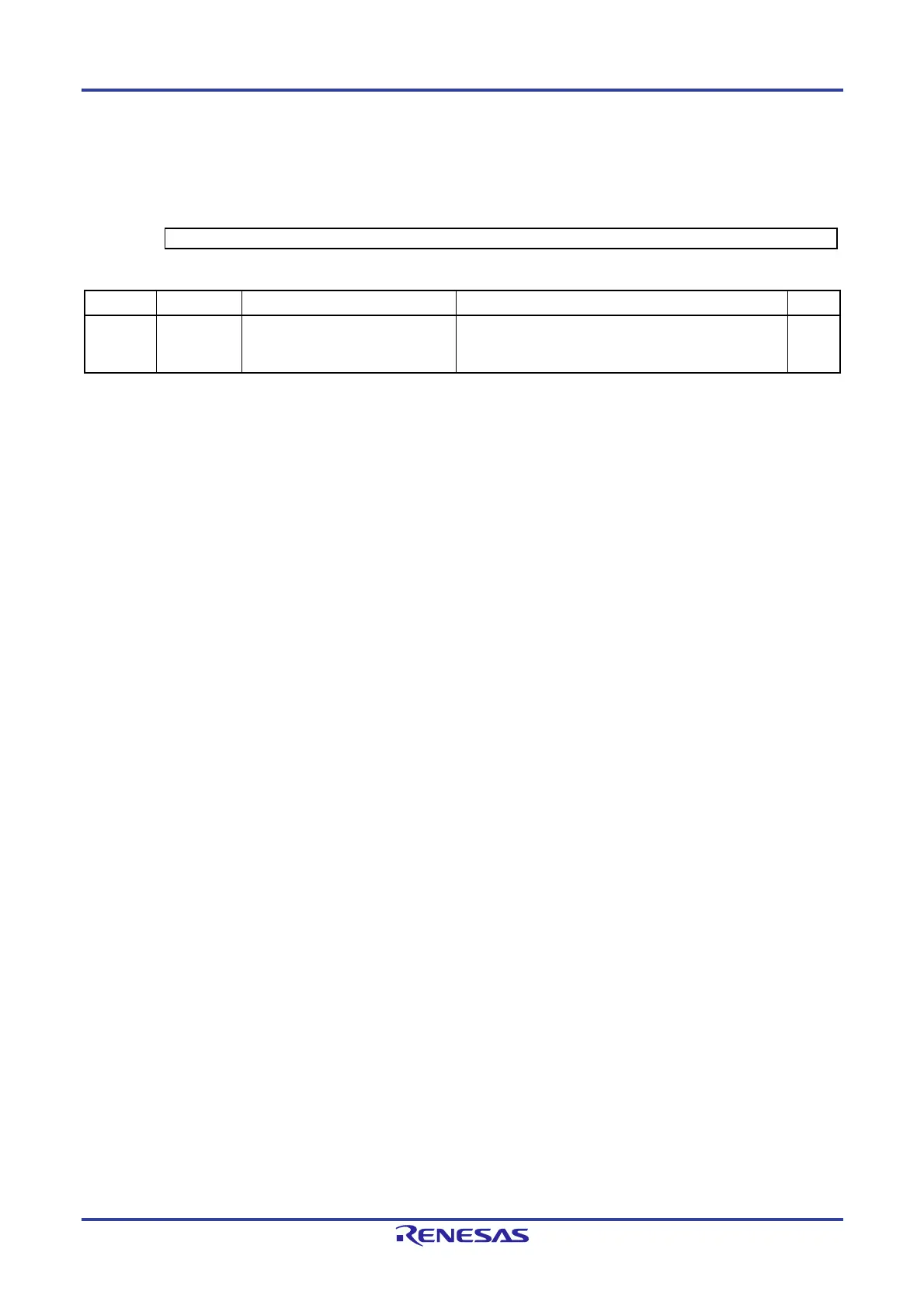

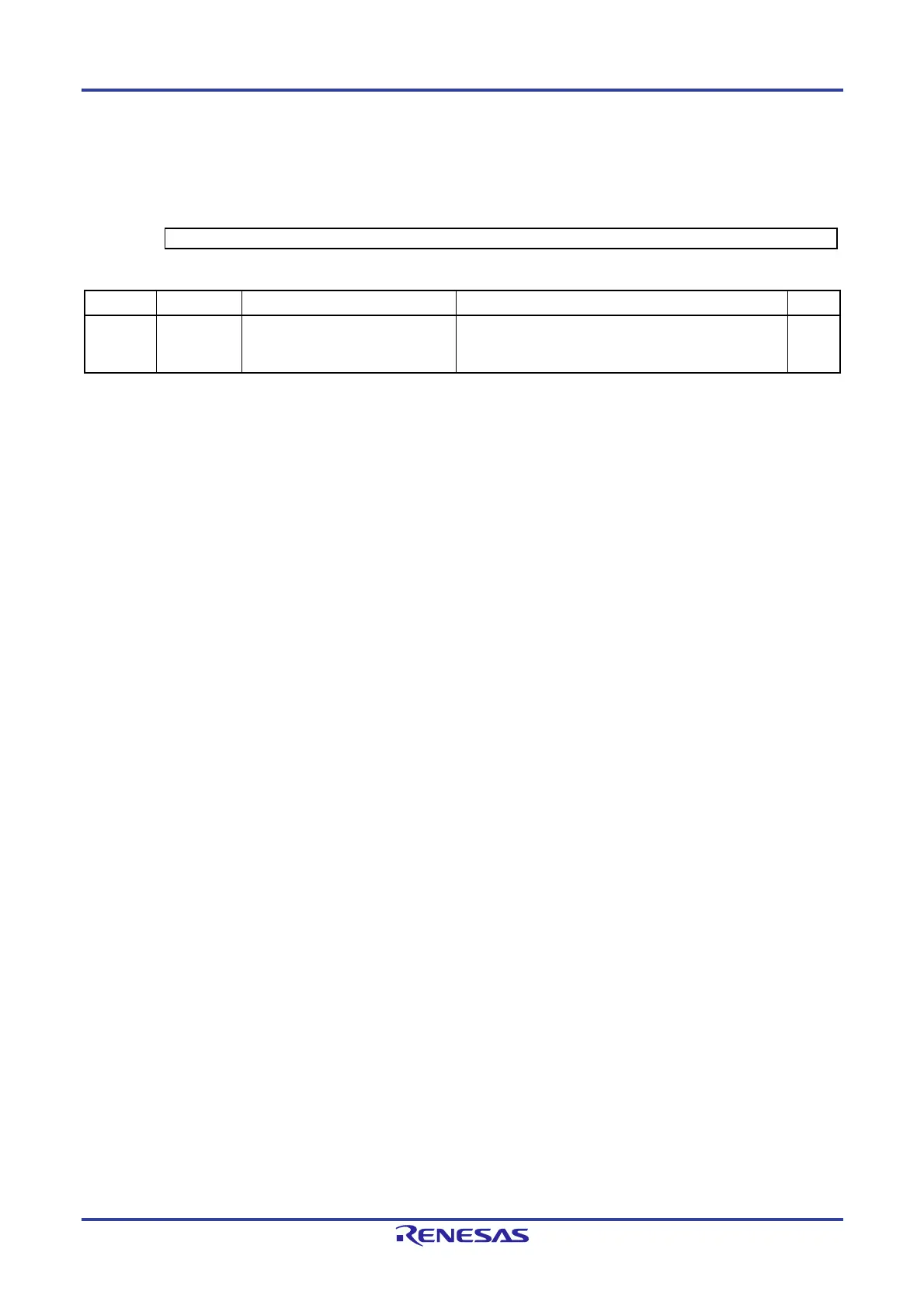

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

TMID[15:0]

After Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit Symbol Bit Name Description R/W

15 to 0 TMID[15:0] Transmit Buffer ID Data L Set standard ID or extended ID.

For standard ID, write an ID to bits 10 to 0 and write 0 to

bits 15 to 11.

R/W

Modify this register when the TMTRM bit in the corresponding TMSTSp register is set to 0 (no transmit request is

present). If this register is linked to any transmit/receive FIFO buffer, do not write data to this register.

This register can be read/written when the RPAGE bit in the GRWCR register is 1.

• TMID[15:0] Bits

These bits are used to set the ID of the message to be transmitted from the transmit buffer.

Loading...

Loading...