RL78/F13, F14 CHAPTER 9 REAL-TIME CLOCK

R01UH0368EJ0210 Rev.2.10 673

Dec 10, 2015

9.3.15 Watch error correction register (SUBCUD)

This register is used to correct the watch with high accuracy when it is slow or fast by changing the value that overflows

from the internal counter (16 bits) to the second count register (SEC) (reference value: 7FFFH).

Set the SUBCUD register by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

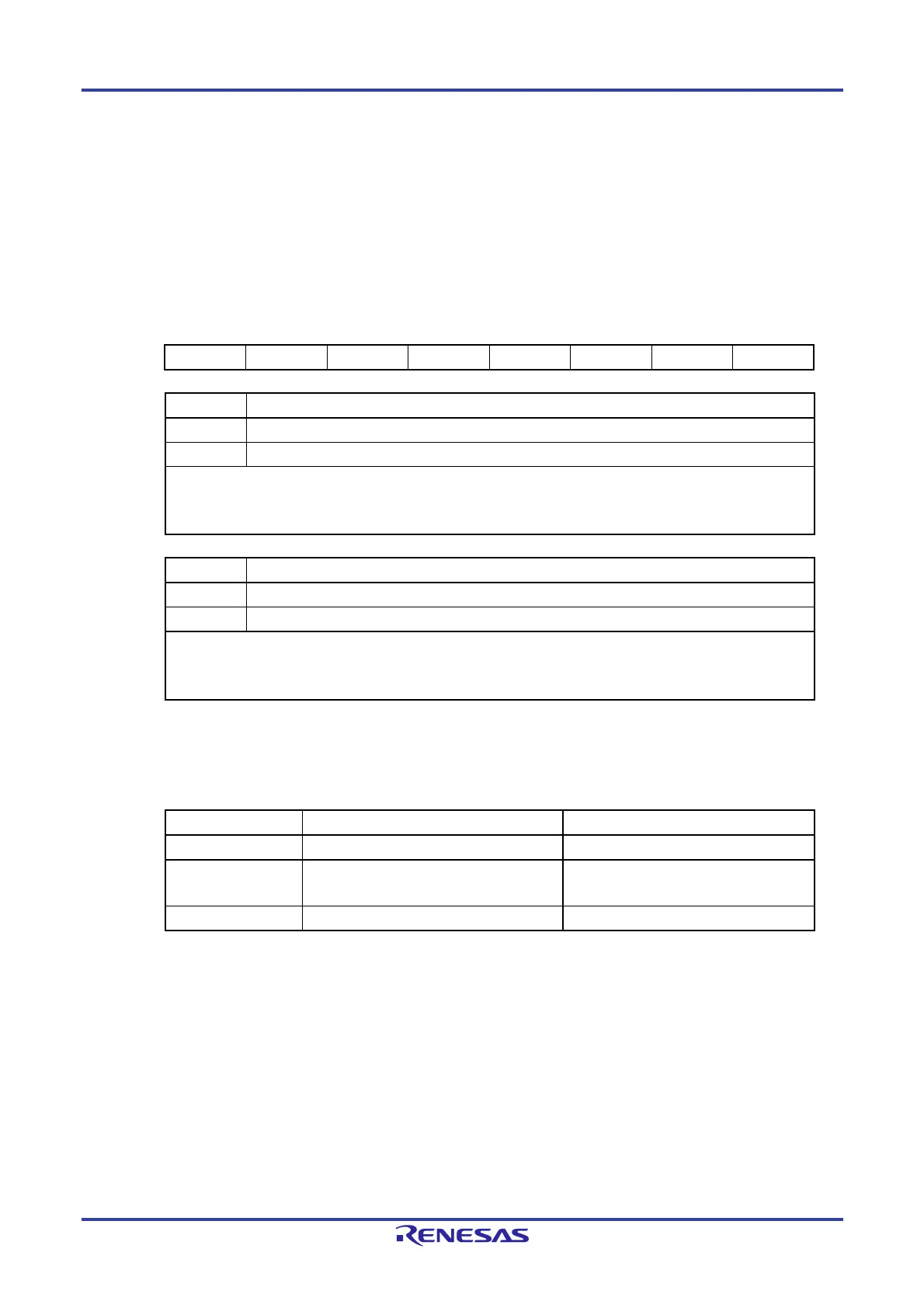

Figure 9-16. Format of Watch Error Correction Register (SUBCUD)

Address: FFF99H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

SUBCUD DEV F12 F5 F4 F3 F2 F1 F0

DEV Setting of watch error correction timing

0 Corrects watch error when the second digits are at 00, 20, or 40 (every 20 seconds).

1 Corrects watch error only when the second digits are at 00 (every 60 seconds).

Writing to the SUBCUD register at the following timing is prohibited.

When DEV = 0 is set: For a period of SEC = 00H, 20H, 40H

When DEV = 1 is set: For a period of SEC = 00H

F12 Setting of watch error correction value

0 Increases by {(F5, F4, F3, F2, F1, F0) – 1} 2.

1 Decreases by {(/F5, /F4, /F3, /F2, /F1, /F0) + 1} 2.

When (F12, F5, F4, F3, F2, F1, F0) = (*, 0, 0, 0, 0, 0, *), the watch error is not corrected.

Range of correction value: (when F12 = 0) 2, 4, 6, 8, … , 120, 122, 124

(when F12 = 1) –2, –4, –6, –8, … , –120, –122, –124

Cautions 1. / of /Fn (n = 0 to 5) means invert.

2. * means 0 or 1.

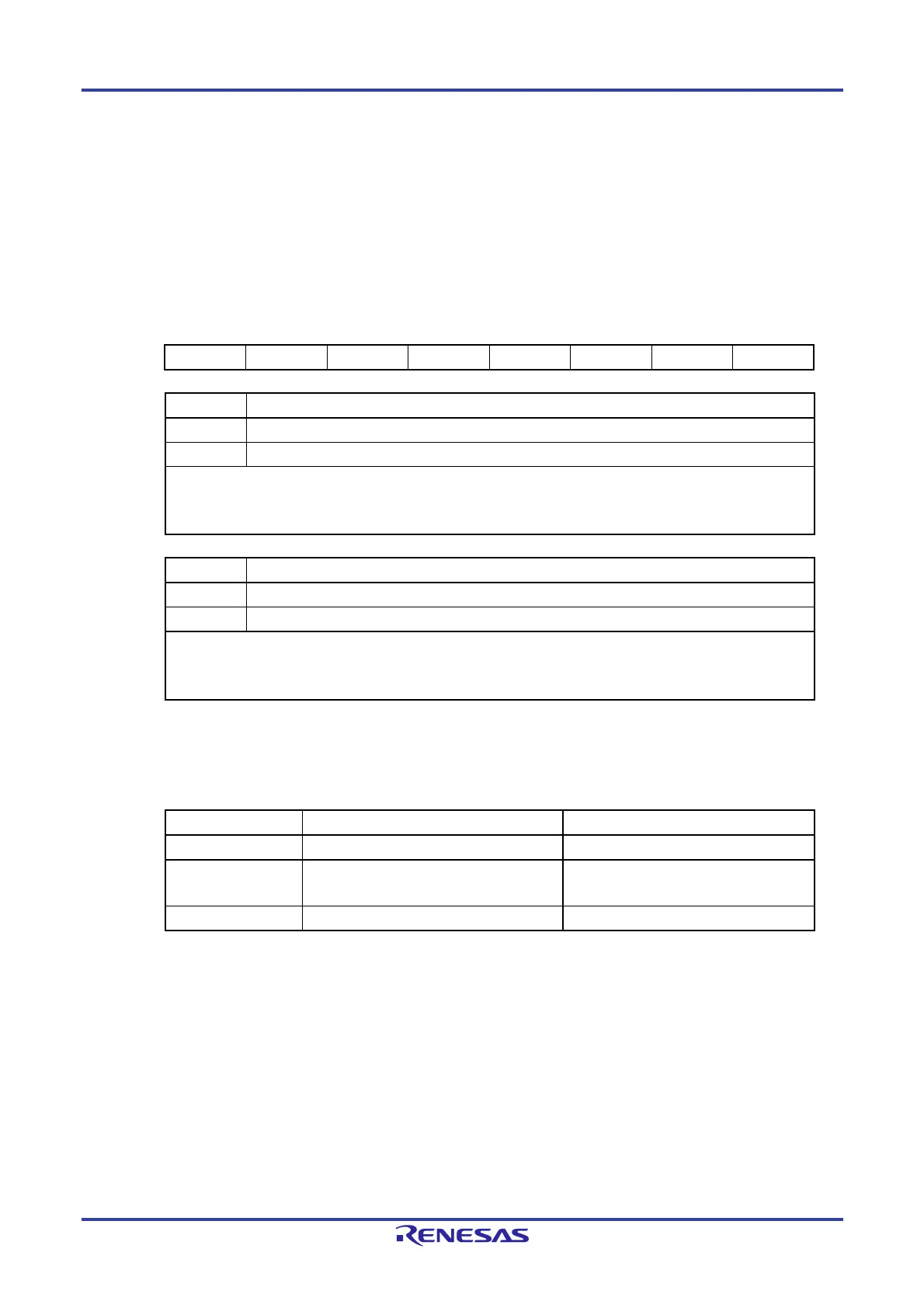

The range of value that can be corrected by using the watch error correction register (SUBCUD) is shown below.

DEV = 0 (correction every 20 seconds) DEV = 1 (correction every 60 seconds)

Correctable range –189.2 ppm to 189.2 ppm –63.1 ppm to 63.1 ppm

Maximum excludes

quantization error

1.53 ppm0.51 ppm

Minimum resolution 3.05 ppm 1.02 ppm

Remark If a correctable range is –63.1 ppm or lower and 63.1 ppm or higher, set 0 to DEV.

Loading...

Loading...