RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 189

Dec 10, 2015

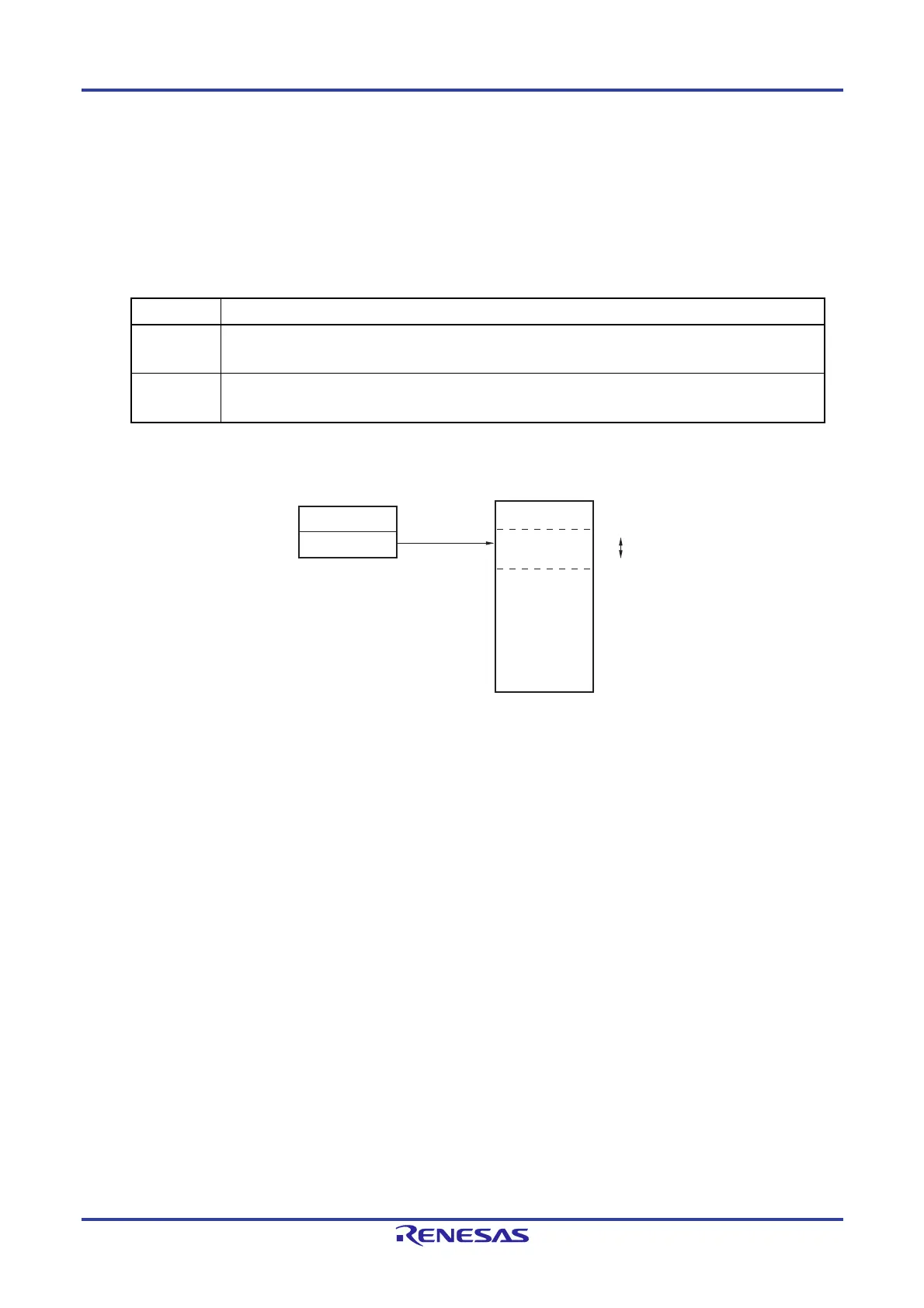

3.4.4 Short direct addressing

[Function]

Short direct addressing directly specifies the target addresses using 8-bit data in the instruction word. This type of

addressing is applied only to the space from FFE20H to FFF1FH.

[Operand format]

Identifier Description

SADDR Label, FFE20H to FFF1FH immediate data, or 0FE20H to 0FF1FH immediate data

(only the space from FFE20H to FFF1FH is specifiable)

SADDRP Label, FFE20H to FFF1FH immediate data, or 0FE20H to 0FF1FH immediate data (even address only)

(only the space from FFE20H to FFF1FH is specifiable)

Figure 3-51. Outline of Short Direct Addressing

Remark SADDR and SADDRP are used to describe the values of addresses FE20H to FF1FH with 16-bit immediate

data (higher 4 bits of actual address are omitted), and the values of addresses FFE20H to FFF1FH with 20-bit

immediate data.

Regardless of whether SADDR or SADDRP is used, addresses within the space from FFE20H to FFF1FH are

specified for the memory.

OP code

Memory

saddr

FFF1FH

FFE20H

saddr

Instruction code

Loading...

Loading...