RL78/F13, F14 CHAPTER 30 FLASH MEMORY

R01UH0368EJ0210 Rev.2.10 1646

Dec 10, 2015

30.8.2 Register controlling data flash memory

30.8.2.1 Data flash control register (DFLCTL)

This register is used to enable or disable accessing to the data flash.

The DFLCTL register is set by a 1-bit or 8-bit memory manipulation instruction.

Reset input sets this register to 00H.

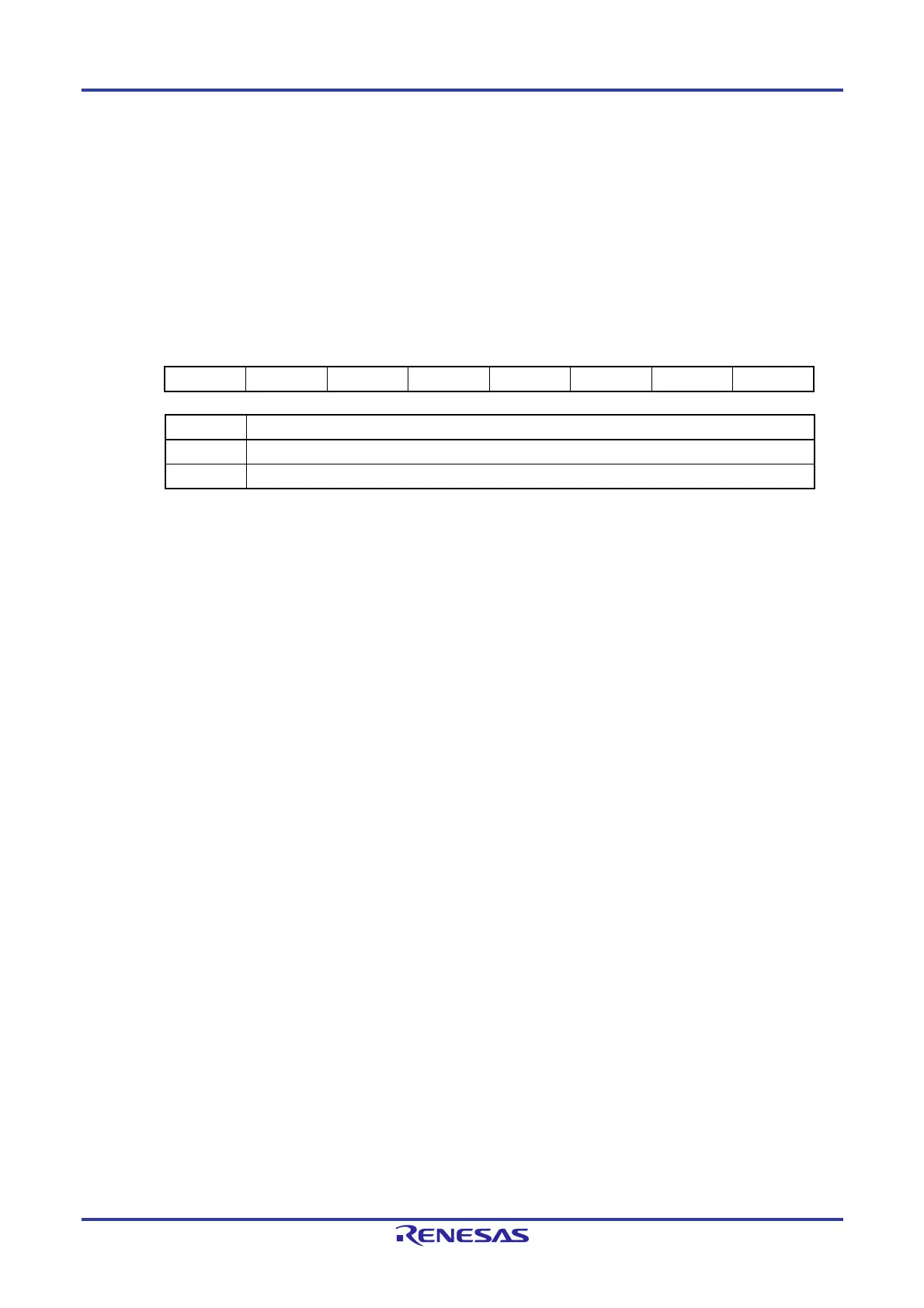

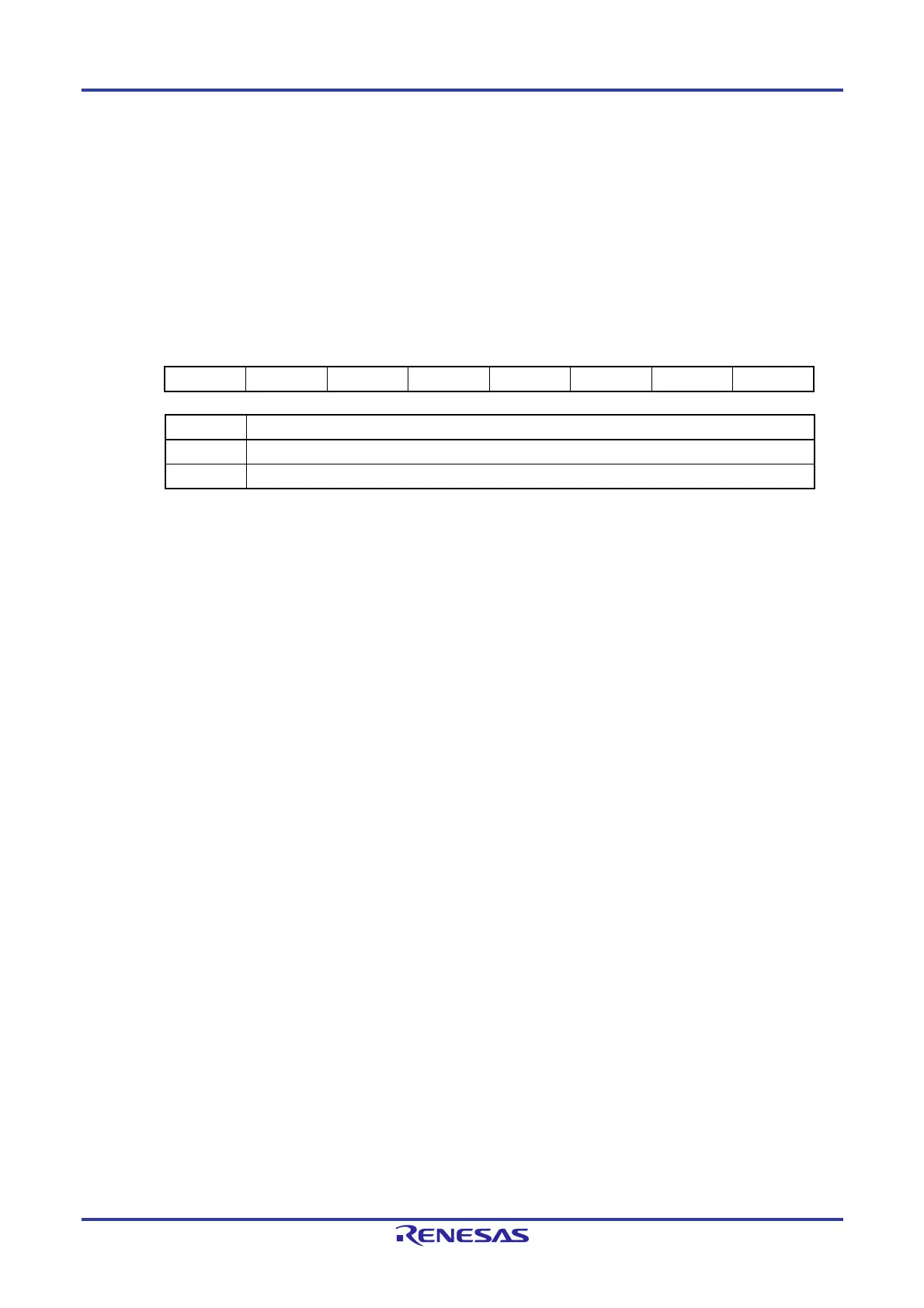

Figure 30-12. Format of Data Flash Control Register (DFLCTL)

Address: F0090H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 <0>

DFLCTL 0 0 0 0 0 0 0 DFLEN

DFLEN Data flash access control

0 Disables data flash access

1 Enables data flash access

Caution Manipulating the DFLCTL register is not possible while rewriting the data flash memory.

Loading...

Loading...