RL78/F13, F14 CHAPTER 21 INTERRUPT FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1512

Dec 10, 2015

21.4.4 Interrupt servicing during division instruction

The RL78/F13 and RL78/F14 handle interrupts during the DIVHU/DIVWU instruction in order to enhance the interrupt

response when a division instruction is executed.

When an interrupt is generated while the DIVHU/DIVWU instruction is executed, the instruction is suspended

After the instruction is suspended, the PC indicates the next instruction after DIVHU/DIVWU

An interrupt is generated by the next instruction

PC-3 is saved in the stack memory to execute the DIVHU/DIVWU instruction again

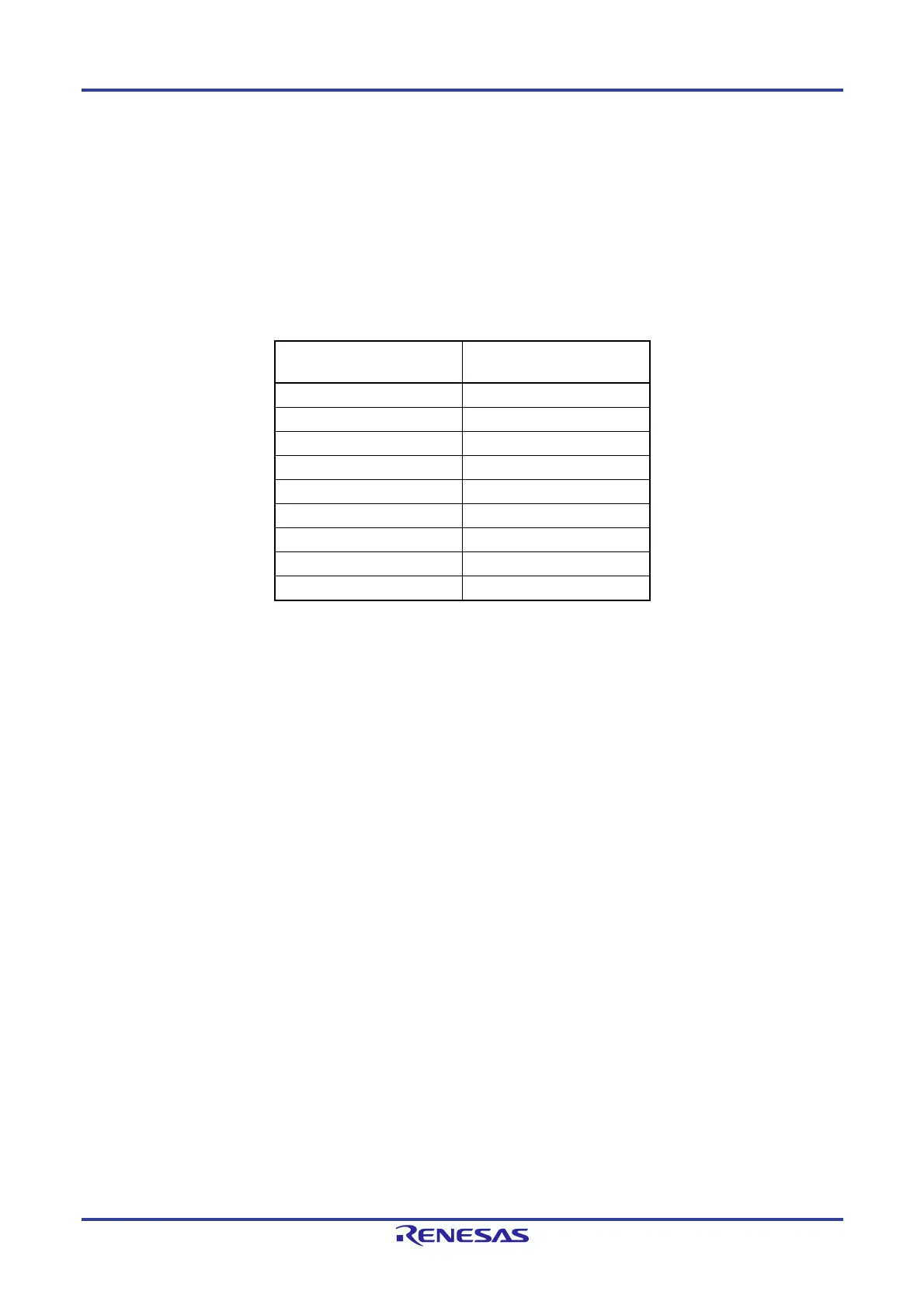

Table 21-6. Normal Interrupt Processing and Interrupt Processing while Executing Division Instructions

Normal interrupt Interrupts while Executing

DIVHU/DIVWU Instruction

(SP-1) PSW (SP-1) PSW

(SP-2) (PC)S (SP-2) (PC-3)S

(SP-3) (PC)H (SP-3) (PC-3)H

(SP-4) (PC)L (SP-4) (PC-3)L

PCS 0000 PCS 0000

PCH (Vector) PCH (Vector)

PCL (Vector) PCL (Vector)

SP SP-4 SP SP-4

IE 0 IE 0

Caution Disable interrupts when executing the DIVHU or DIVWU instruction in an interrupt servicing routine.

Alternatively, unless they are executed in the RAM area, note that execution of a DIVHU or DIVWU

instruction is possible even with interrupts enabled as long as a NOP instruction is added immediately

after the DIVHU or DIVWU instruction in the assembly language source code. The following compilers

automatically add a NOP instruction immediately after any DIVHU or DIVWU instruction output during

the build process.

- V. 1.71 and later versions of the CA78K0R (Renesas Electronics compiler), for both C and

assembly language source code

- Service pack 1.40.6 and later versions of the EWRL78 (IAR compiler), for C language source code

- GNURL78 (KPIT compiler), for C language source code

The AX, BC, DE, and HL registers are used for DIVHU/DIVWU. For the interrupt processing, save these registers in the

stack memory.

<R>

Loading...

Loading...