RL78/F13, F14 CHAPTER 5 CLOCK GENERATOR

R01UH0368EJ0210 Rev.2.10 407

Dec 10, 2015

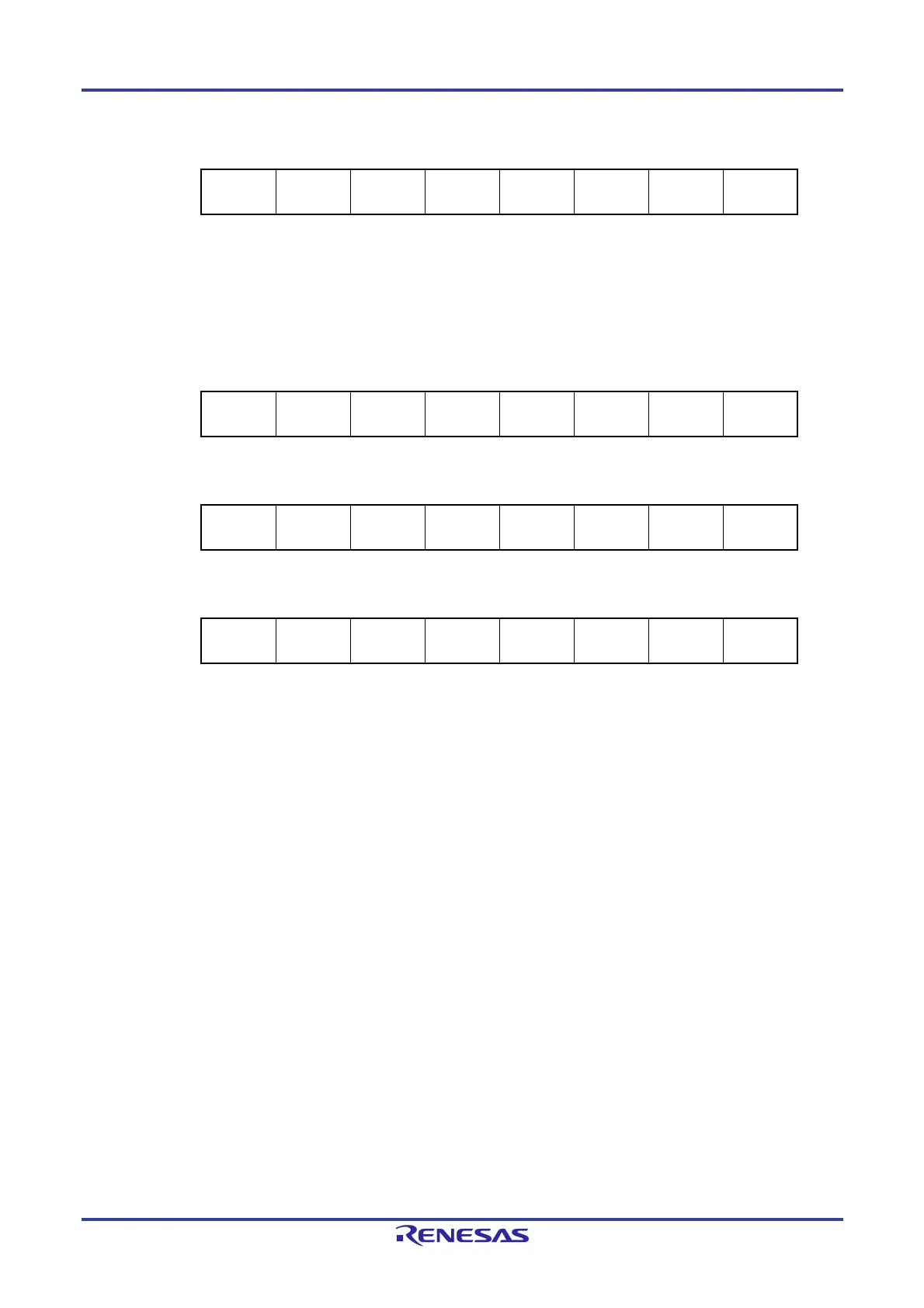

<10> Confirm that the PLL-clock-selected mode is selected (SELPLLS = 1) with the SELPLLS bit of the PLLSTS register.

7 6 5 4 3 2 1 0

PLLSTS

LOCK

1

0

0

0

SELPLLS

1

0

0

0

(2) Examples of procedure for stopping PLL clock

There is the following method to stop the PLL clock.

Set the PLLON bit to 0 to stop the PLL clock.

<1> Select the PLL clock mode with the SELPLL bit of the PLLCTL register.

Clear the SELPLL bit to 0 to select the clock through mode (f

PLL = fMAIN).

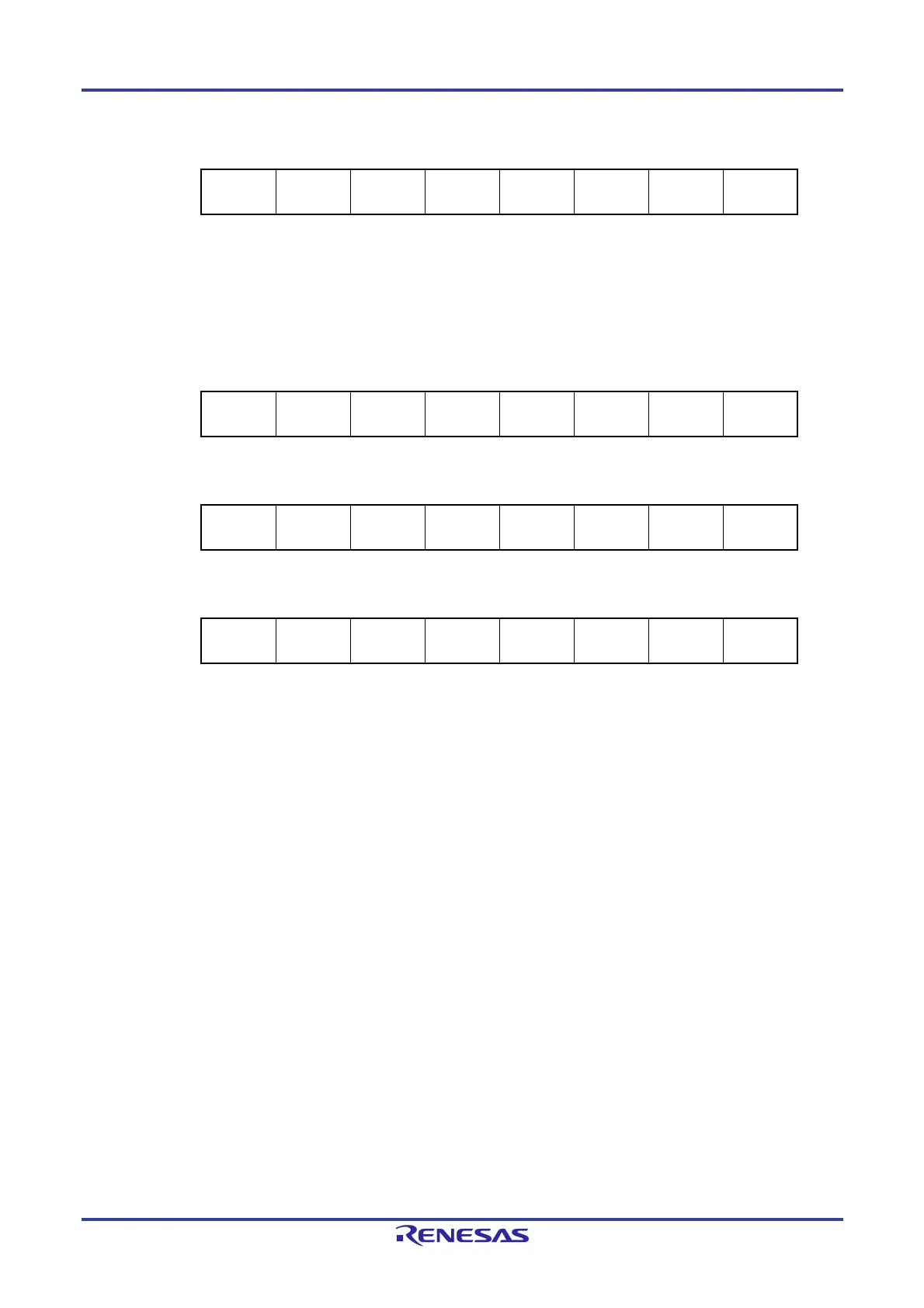

7 6 5 4 3 2 1 0

PLLCTL

LCKSEL1

0/1

LCKSEL0

0/1

PLLDIV1

0/1

PLLDIV0

0/1

0

SELPLL

0

PLLMUL

0/1

PLLON

1

<2> Confirm that the clock through mode is selected (SELPLLS = 0) with the SELPLLS bit of the PLLSTS register.

7 6 5 4 3 2 1 0

PLLSTS

LOCK

0/1

0

0

0

SELPLLS

0

0

0

0

<3> Clear the PLLON bit of the PLLCTL register to 0 to stop oscillation of the PLL clock.

7 6 5 4 3 2 1 0

PLLCTL

LCKSEL1

0/1

LCKSEL0

0/1

PLLDIV1

0/1

PLLDIV0

0/1

0

SELPLL

0

PLLMUL

0/1

PLLON

0

(3) Caution when restarting the PLL clock after being stopped

In a case of restarting the PLL clock after it has been stopped, wait for at least 4 s after the PLL circuit was stopped

before restarting operation.

Loading...

Loading...