RL78/F13, F14 CHAPTER 15 SERIAL ARRAY UNIT

R01UH0368EJ0210 Rev.2.10 1004

Dec 10, 2015

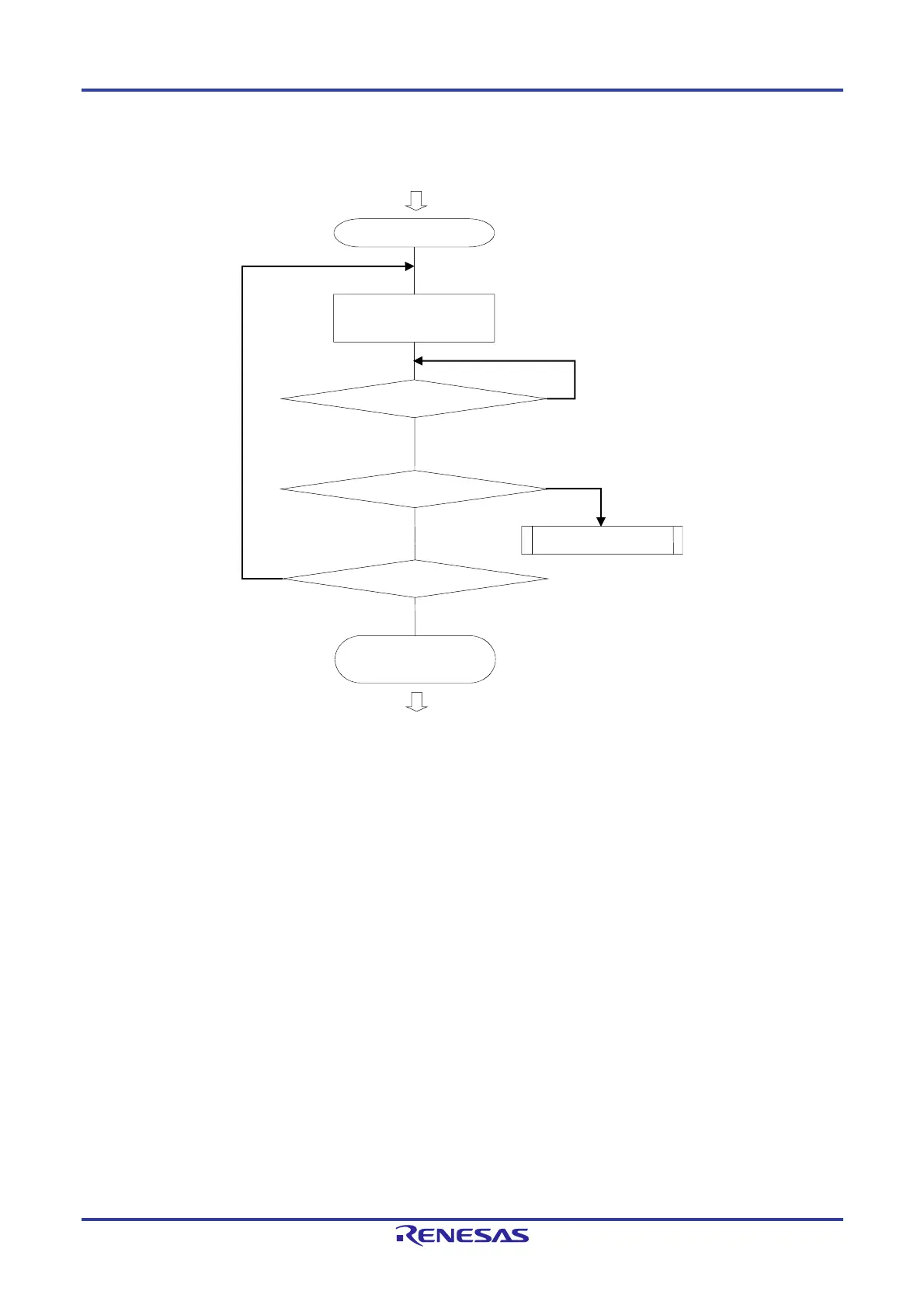

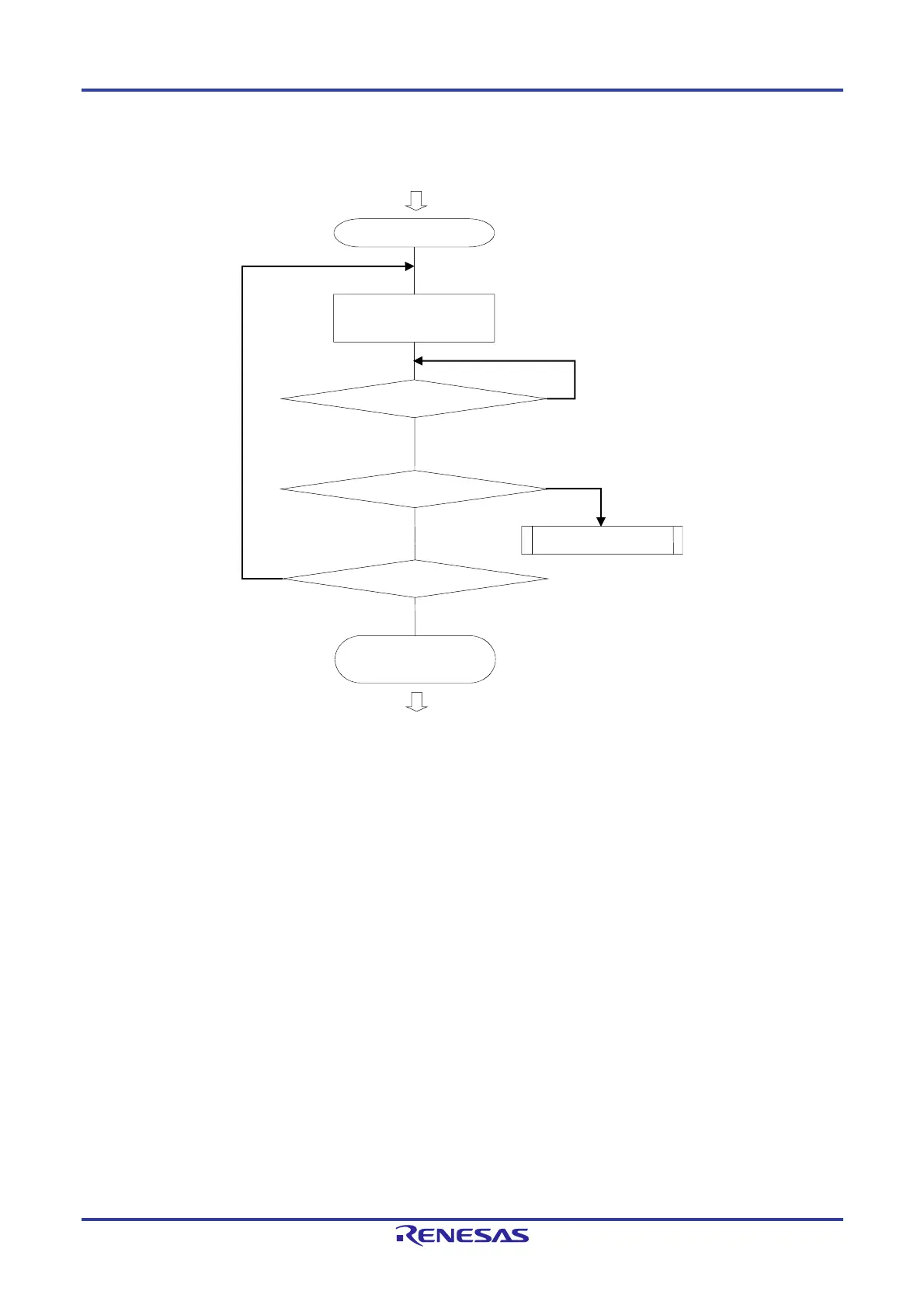

Figure 15-149. Flowchart of Data Transmission

Remark m: Unit number (m = 0, 1), n: Channel number (n = 0, 1), r: IIC number (r = 00, 01, 10, 11),

mn = 00, 01, 10, 11

Starting data transmission

Data transmission

completed

Transfer end interrupt

enerated?

No

Yes

Writing data to the SDRmn

register

No

Yes

ACK reception error

op con

on genera

on

Data transfer completed?

Yes

No

Address field

transmission completed

Parity error (ACK error) flag

PEFmn = 1 ?

Loading...

Loading...