RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1220

Dec 10, 2015

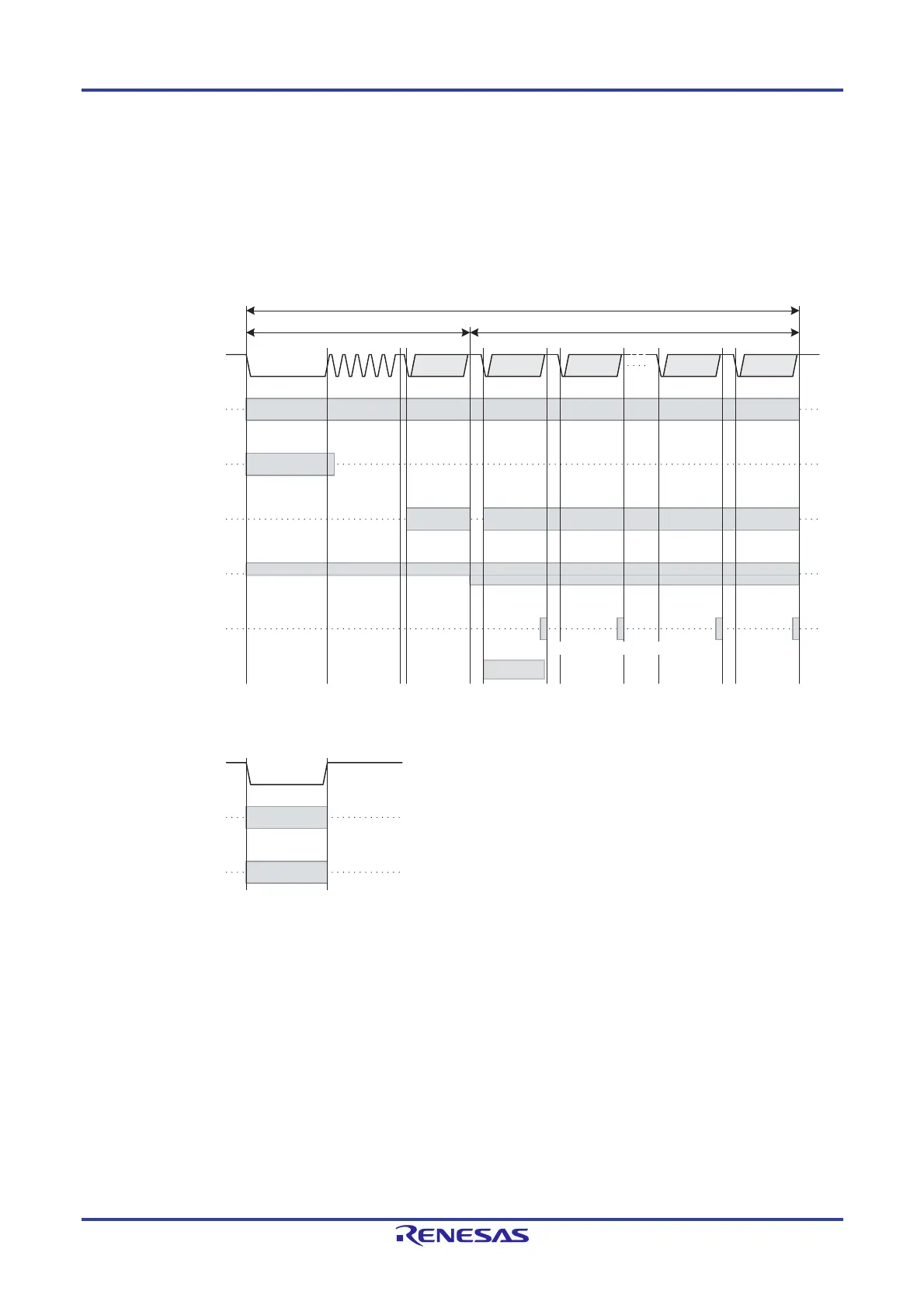

(b) Target Time Area for LIN Error Detection

Figure 17-20 shows the time domain in which the LIN/UART module in master mode performs monitoring for

error detection.

Figure 17-20. Target Time Area for LIN Error Detection (LIN Master Mode)

<Wake-up transmission>

Wake-up

Bit error

Data 1 Data 2 Data 8 Checksum

Header Response

Frame

Sync field

ID field

Bit error

In transmission only

In reception only

<Frame transmission/reception>

Frame timeout error

Only in transmission

of break field and

break delimiter

Break field

Response timeout error

Only stop bit in reception

Physical bus

error

Response

preparation error

Checksum error

Physical bus error

Only in reception

with enhance

checksum mode

selected

Framing error

Loading...

Loading...