RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1386

Dec 10, 2015

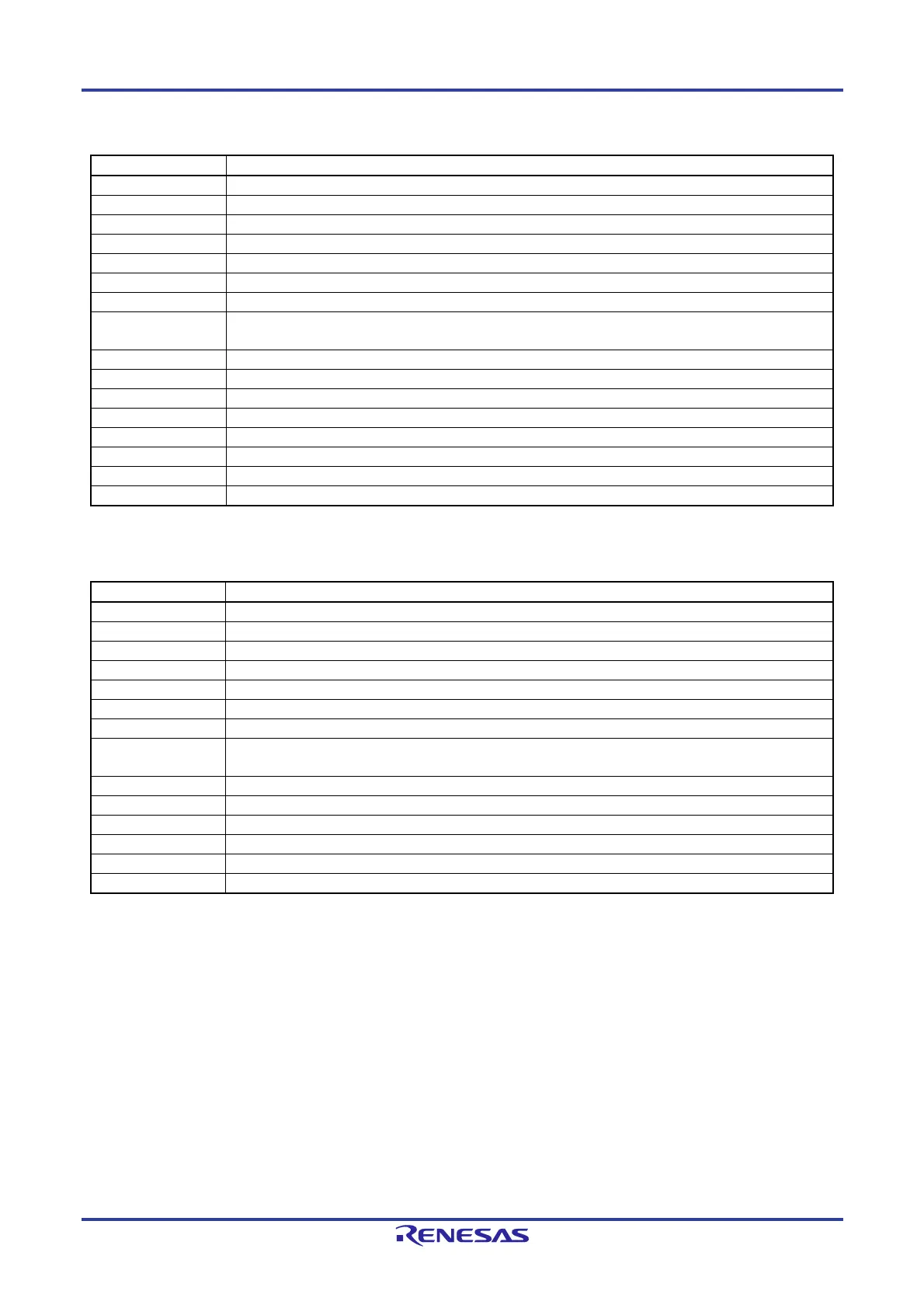

Table 18-9. Registers Initialized in Global Reset Mode or Channel Reset Mode

Register Bit / Flag

CiCTRL register CHMDC[1:0]

CiCTRH register CTMS[1:0], CTME

CiSTSL register CHLTSTS, EPSTS, BOSTS, TRMSTS, RECSTS, COMSTS

CiSTSH register REC[7:0], TEC[7:0]

CiERFLL register ADERR, B0ERR, B1ERR, CERR, AERR, FERR, SERR, ALF, BLF, OVLF, BORF, BOEF, EPF, EWF, BEF

CiERFLH register CRCREG[14:0]

CFCCLk register When transmit/receive FIFO buffer is in transmit mode: CFE

CFSTSk register When transmit/receive FIFO buffer is in transmit mode: CFMC[5:0], CFTXIF, CFRXIF, CFMLT, CFFLL,

CFEMP

TMCp register TMOM, TMTAR, TMTR

TMSTSp register TMTARM, TMTRM, TMTRF[1:0], TMTSTS

TMTRSTS register TMTRSTSp

TMTCSTS register TMTCSTSp

TMTASTS register TMTASTSp

THLCCi register THLE

THLSTSi register THLMC[3:0], THLIF, THLELT, THLFLL, THLEMP

GTINTSTS register THIFi, CFTIFi, TAIFi, TSIFi

Remark i = 0, k = 0, p = 0 to 3

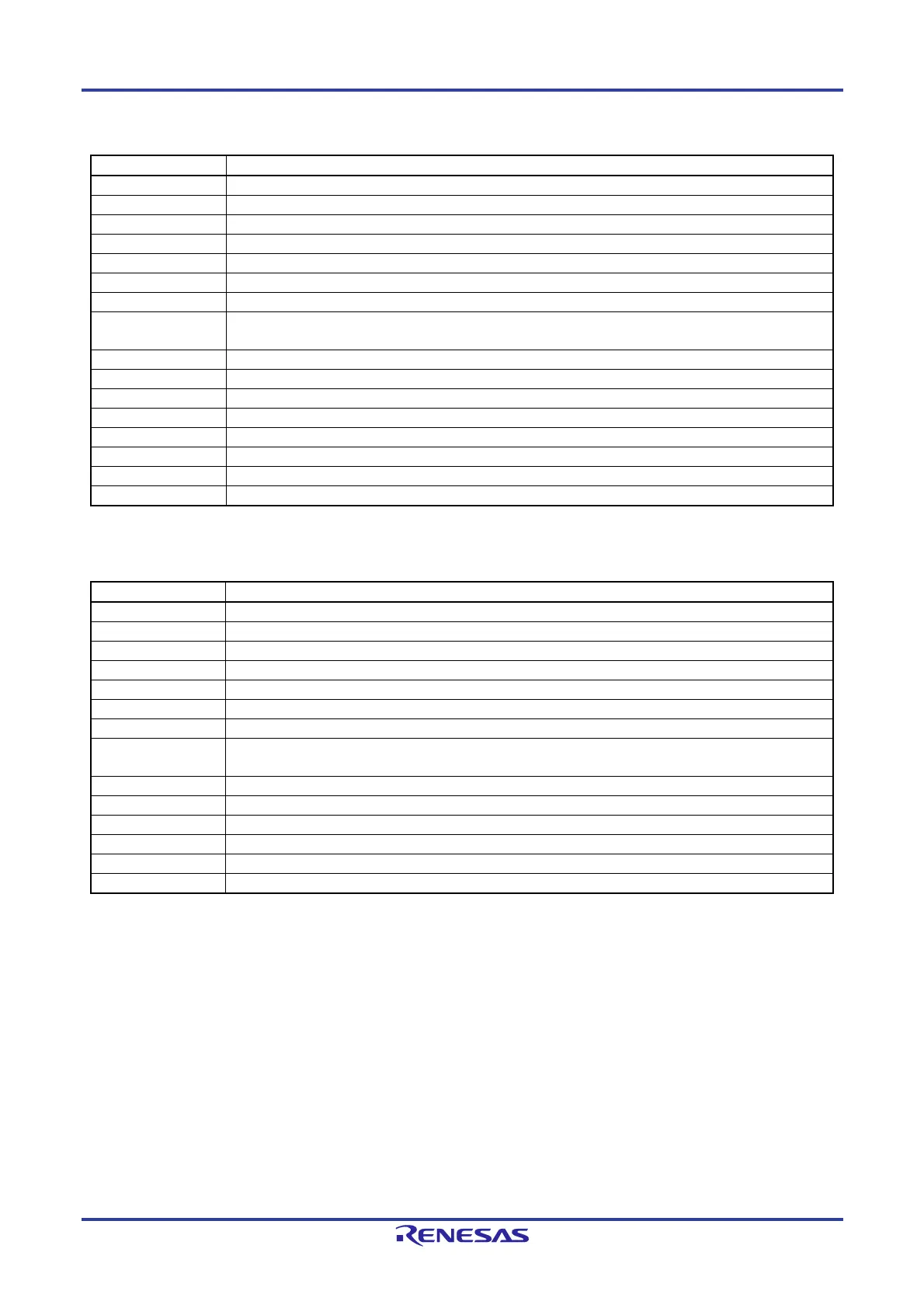

Table 18-10. Registers Initialized Only in Global Reset Mode

Register Bit / Flag

GSTS register GHLTSTS

GERFLL register THLES, MES, DEF

GTSC register TS[15:0]

RMND0 register RMNSn

RFCCm register RFE

RFSTSm register RFMC[5:0], RFIF, RFMLT, RFFLL, RFEMP

CFCCLk register When transmit/receive FIFO buffer is in receive mode: CFE

CFSTSk register When transmit/receive FIFO buffer is in receive mode: CFMC[5:0], CFTXIF, CFRXIF, CFMLT, CFFLL,

CFEMP

RFMSTS register RFmMLT

CFMSTS register CFkMLT

RFISTS register RFmIF

CFISTS register CFkIF

GTSTCFG register RTMPS[2:0]

GTSTCTRL register RTME

Remark k = 0, m = 0, 1, n = 0 to 15

Loading...

Loading...