RL78/F13, F14 CHAPTER 19 DTC

R01UH0368EJ0210 Rev.2.10 1433

Dec 10, 2015

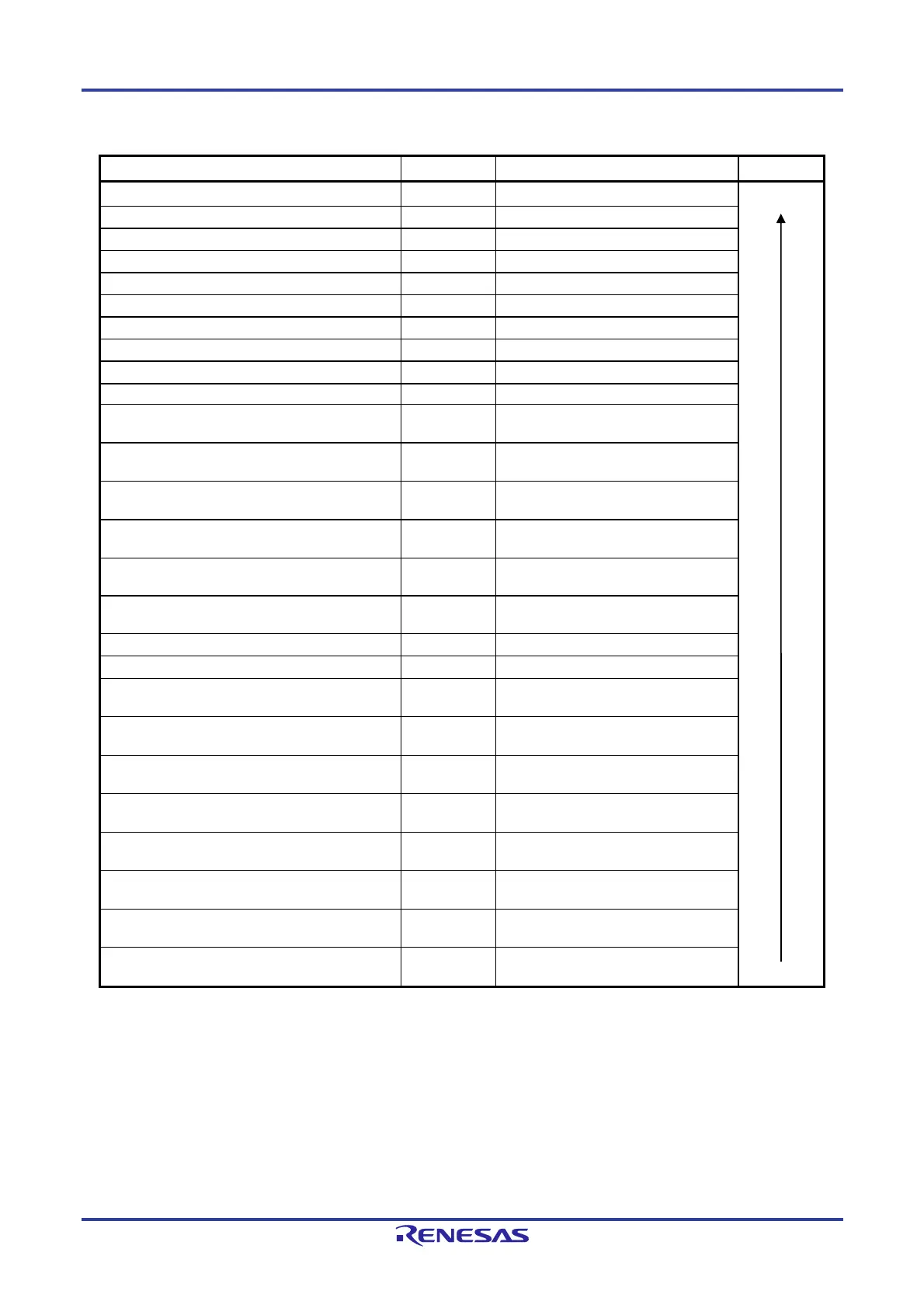

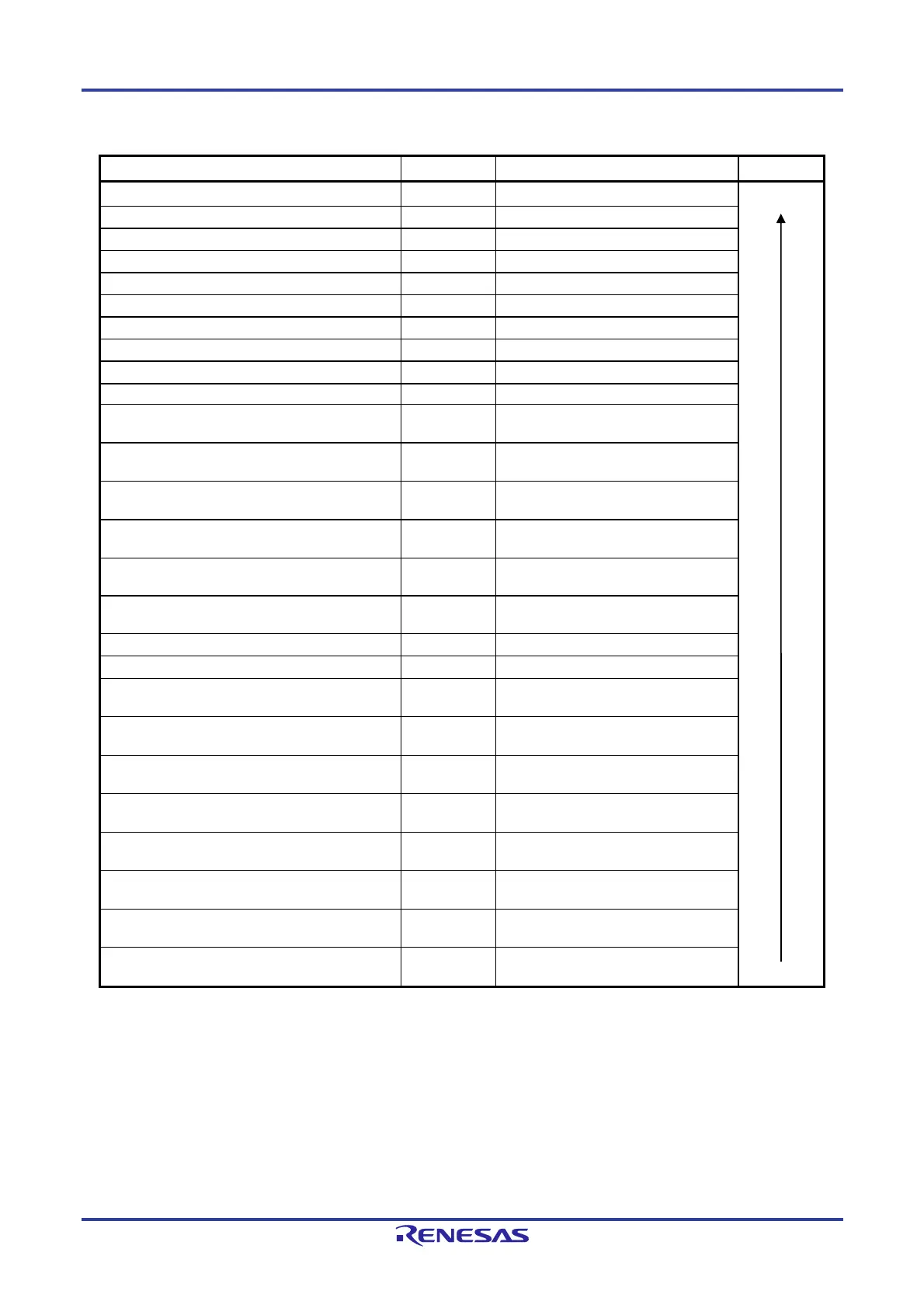

Table 19-5. DTC Activation Sources and DTC Vector Addresses (1/2)

Interrupt Request Source Source No. DTC Vector Address Priority

Reserved 0 Address set in DTCBAR register +00H

Highest

INTP0

1 Address set in DTCBAR register +01H

INTP1

2 Address set in DTCBAR register +02H

INTP2

3 Address set in DTCBAR register +03H

INTP3

4 Address set in DTCBAR register +04H

INTP4

5 Address set in DTCBAR register +05H

INTP5

Note 1

6 Address set in DTCBAR register +06H

INTP6

Notes 1, 2

7 Address set in DTCBAR register +07H

Key input 8 Address set in DTCBAR register +08H

A/D conversion end 9 Address set in DTCBAR register +09H

UART0 reception transfer end/CSI01 transfer end

or buffer empty/IIC01 transfer end

10

Address set in DTCBAR register +0AH

UART0 transmission transfer end/CSI00 transfer

end or buffer empty/IIC00 transfer end

11

Address set in DTCBAR register +0BH

UART1 reception transfer end/CSI11 transfer end

or buffer empty/IIC11 transfer end

Notes 3, 4

12

Address set in DTCBAR register +0CH

UART1 transmission transfer end/CSI10 transfer

end or buffer empty/IIC10 transfer end

Note 3

13

Address set in DTCBAR register +0DH

LIN0 reception end 14

Address set in DTCBAR register +0EH

LIN0 transmission start/end 15

Address set in DTCBAR register +0FH

CAN reception end

Note 5

16 Address set in DTCBAR register +10H

Reserved 17 Address set in DTCBAR register +11H

End of channel 0 of timer array unit 0 count or

capture

18 Address set in DTCBAR register +12H

End of channel 1 of timer array unit 0 count or

capture

19 Address set in DTCBAR register +13H

End of channel 2 of timer array unit 0 count or

capture

20 Address set in DTCBAR register +14H

End of channel 3 of timer array unit 0 count or

capture

21 Address set in DTCBAR register +15H

End of channel 4 of timer array unit 0 count or

capture

22 Address set in DTCBAR register +16H

End of channel 5 of timer array unit 0 count or

capture

23 Address set in DTCBAR register +17H

End of channel 6 of timer array unit 0 count or

capture

24 Address set in DTCBAR register +18H

End of channel 7 of timer array unit 0 count or

capture

25 Address set in DTCBAR register +19H

(Notes and Remark are listed on the next page.)

Loading...

Loading...