RL78/F13, F14 CHAPTER 21 INTERRUPT FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1506

Dec 10, 2015

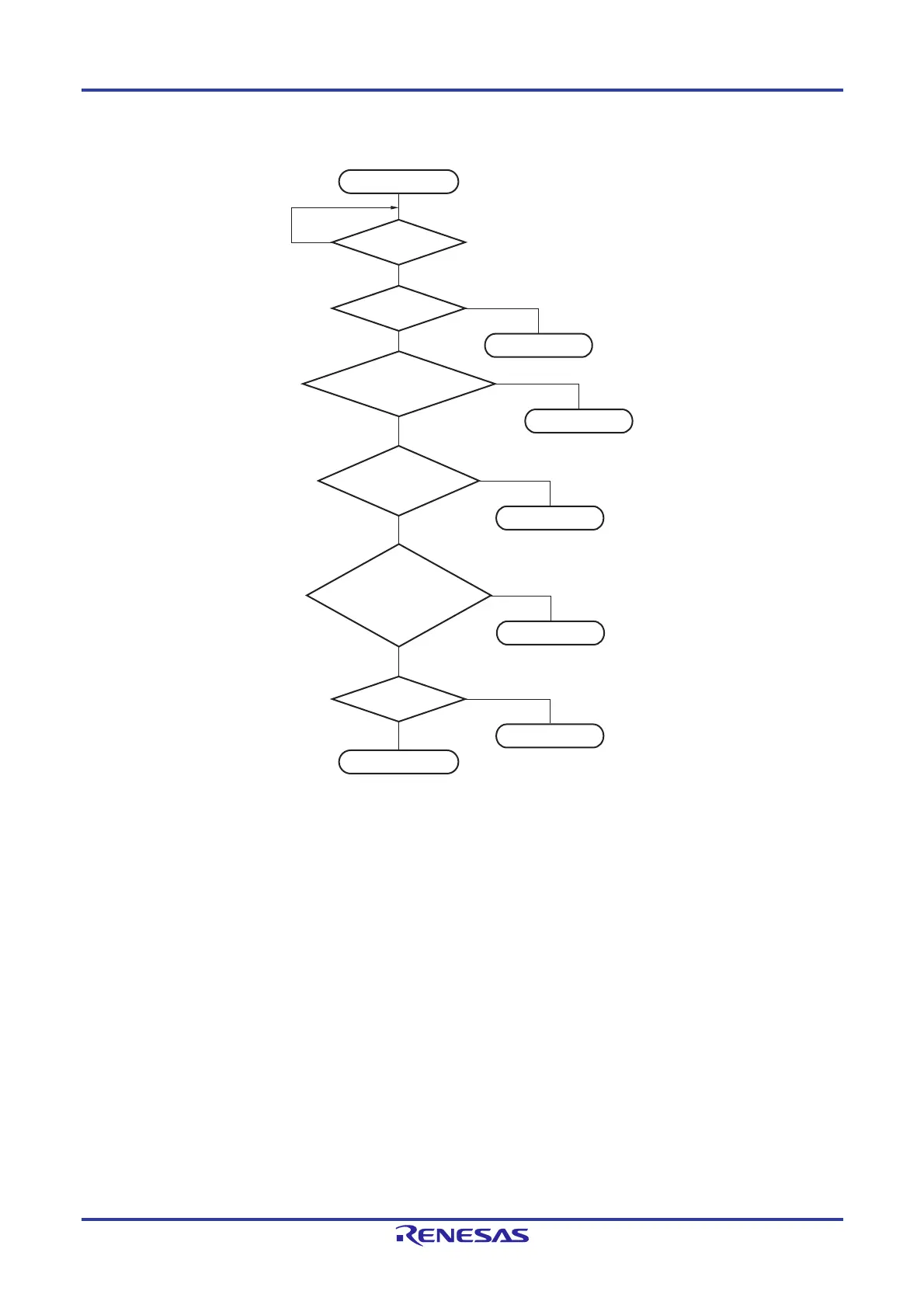

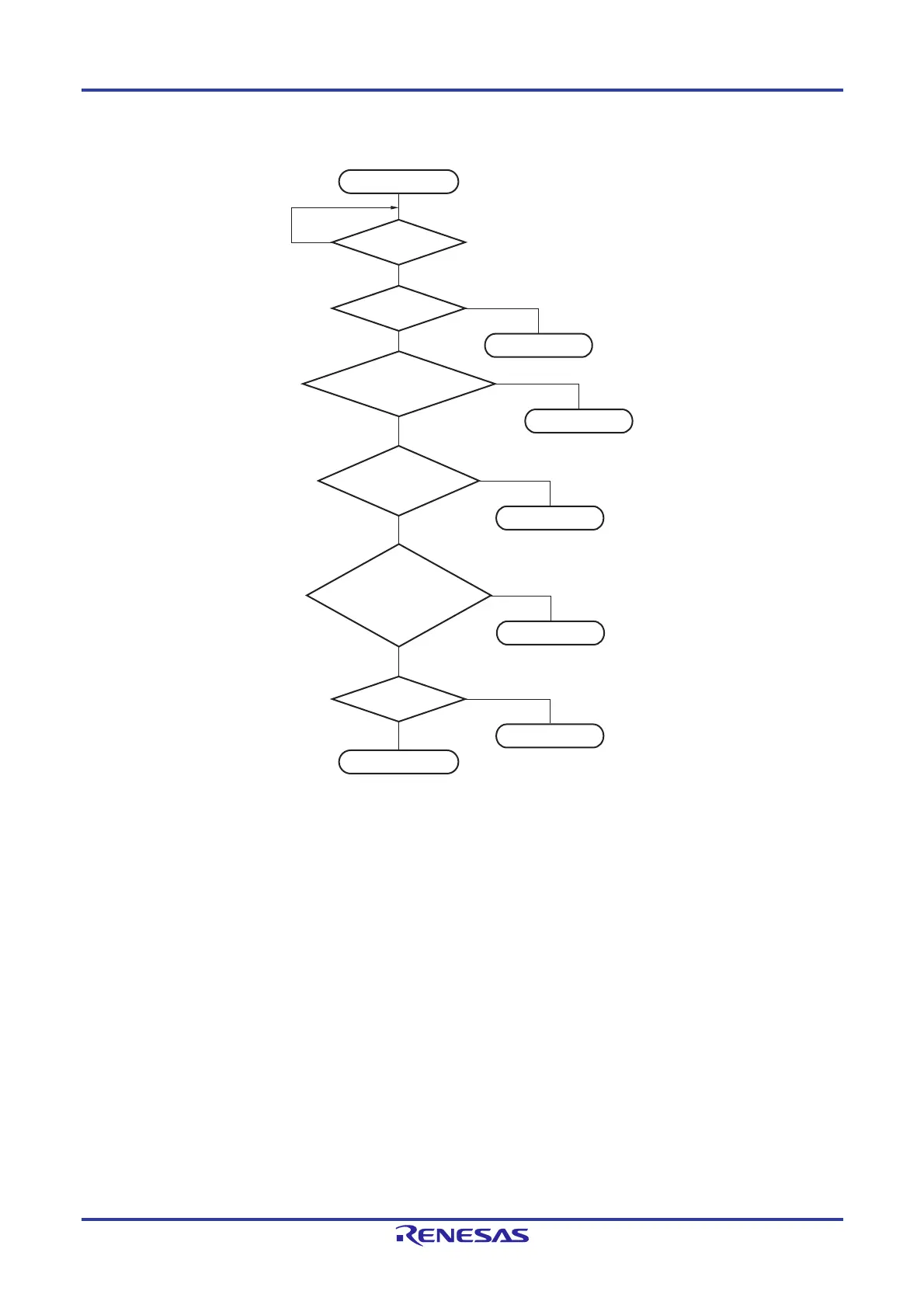

Figure 21-11. Interrupt Request Acknowledgment Processing Algorithm

IF: Interrupt request flag

MK: Interrupt mask flag

PR0: Priority specification flag 0

PR1: Priority specification flag 1

IE: Flag that controls acknowledgment of maskable interrupt request (1 = Enable, 0 = Disable)

ISP0, ISP1: Flag that indicates the priority level of the interrupt currently being serviced

Note For the default priority, see Table 21-1 Interrupt Source List.

Yes

No

Yes

No

Yes

No

No

Yes

No

IE = 1?

Vectored interrupt servicing

Start

××IF = 1?

××MK = 0?

(××PR

1,

××PR

0)

(ISP1, ISP0)

Yes (interrupt request generation)

No (Low priority)

Interrupt request held pending

Interrupt request held pending

Interrupt request held pending

Interrupt request held pending

Interrupt request held pending

Higher priority

than other interrupt requests

simultaneously

generated?

Higher default priority

Note

than other interrupt requests

simultaneously

generated?

≥

Yes (High

priority

)

Loading...

Loading...