RL78/F13, F14 CHAPTER 23 STANDBY FUNCTION

R01UH0368EJ0210 Rev.2.10 1526

Dec 10, 2015

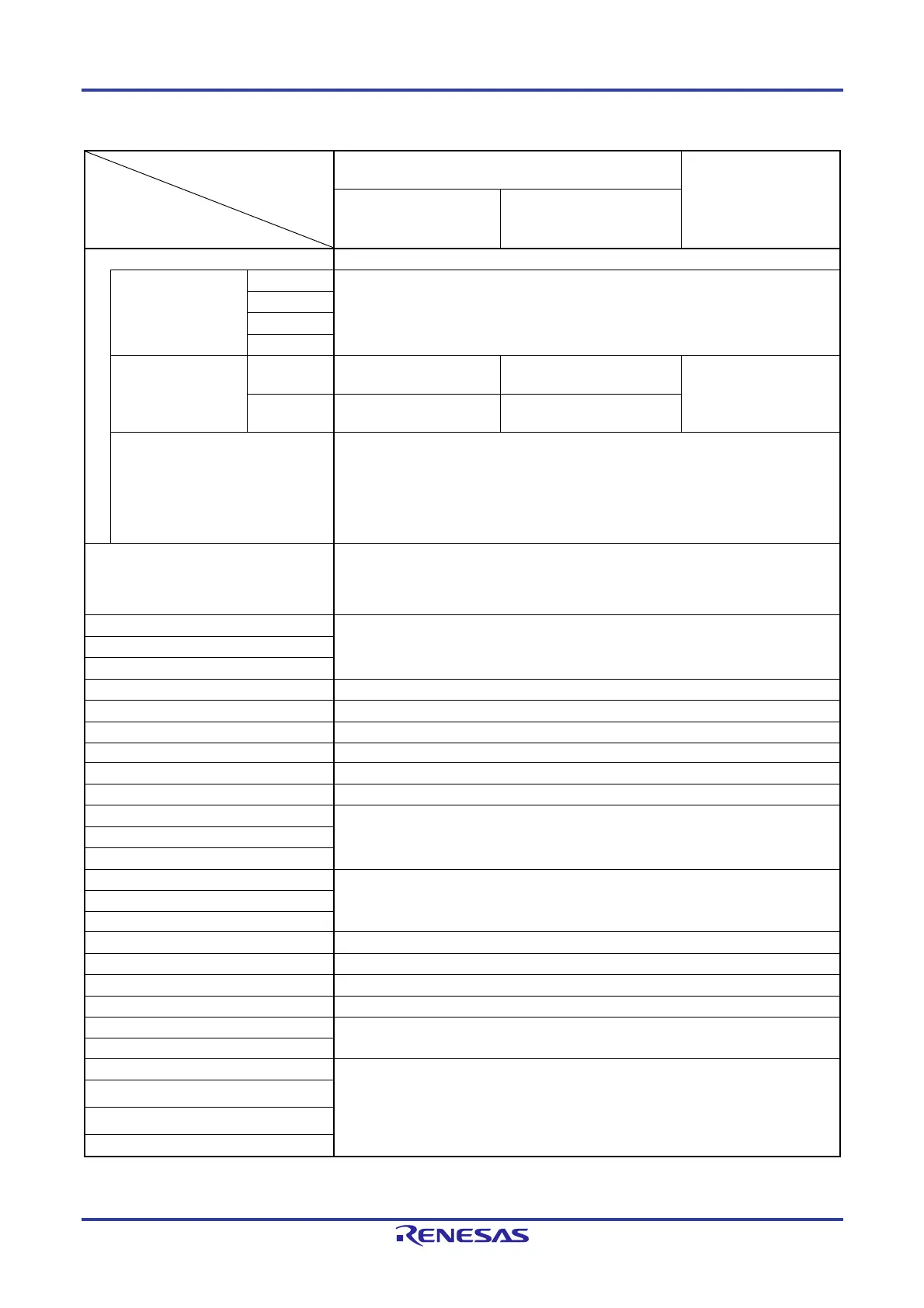

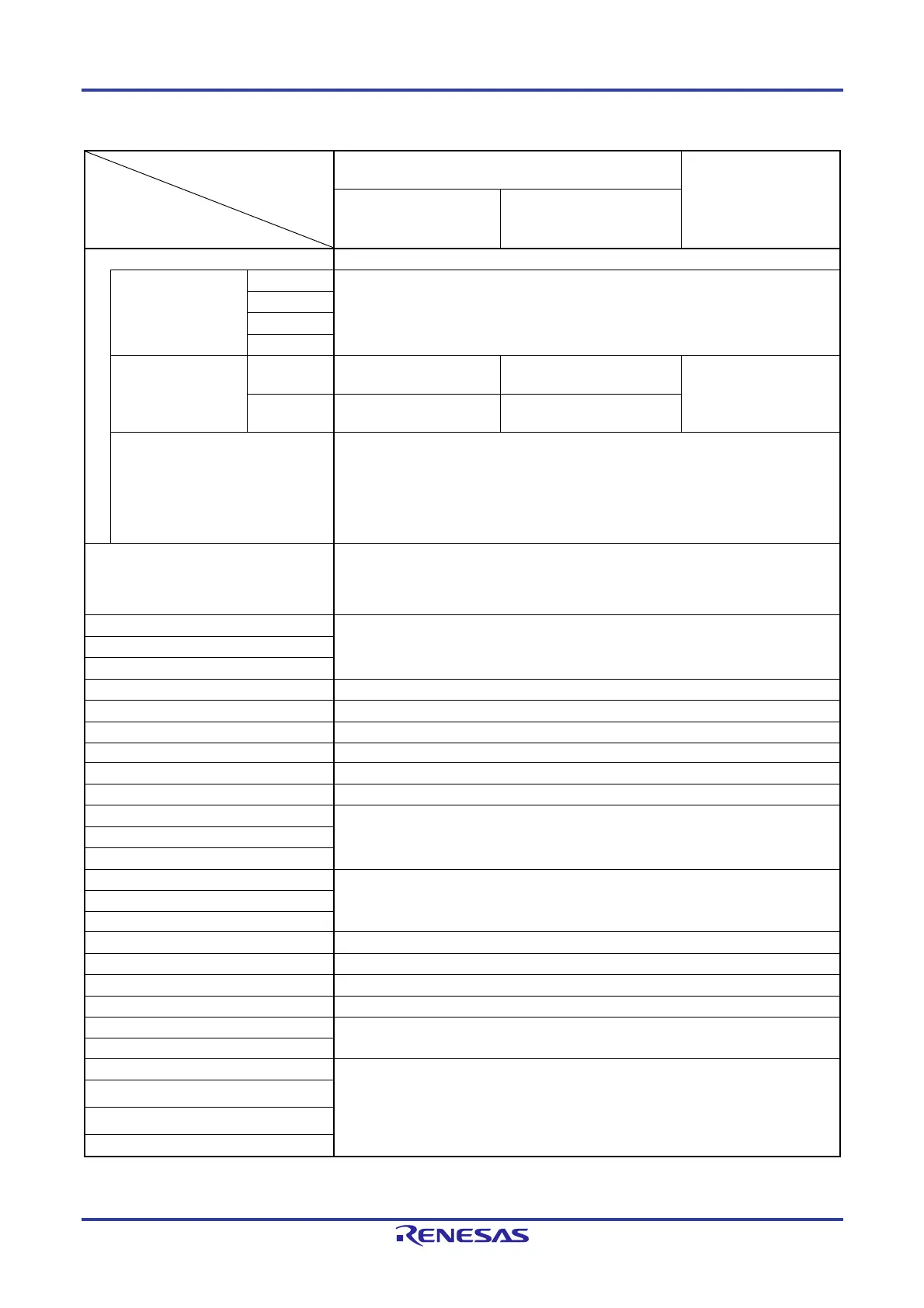

Table 23-1. Operating Statuses in HALT Mode (2/2)

HALT Mode Setting

Item

When HALT Instruction Is Executed While CPU Is Operating

on Subsystem Clock

When HALT Instruction Is

Executed While CPU Is

Operating on Low-speed

On-chip Oscillator Clock

(f

IL)

When CPU Is Operating on

XT1 Clock (f

XT)

When CPU Is Operating on

External

Subsystem Clock (f

EXS)

System clock Clock supply to the CPU is stopped

Main system clock fIH Operation disabled

fX

fEX

fPLL

Subsystem clock fXT Operation continues

(cannot be stopped)

Cannot operate Cannot operate

fEXS Cannot operate Operation continues (cannot

be stopped)

fIL

Set by bit 1 (HPIEN) of on-chip debug option byte (000C3H/020C3H), bit 0 (SELLOSC) of

the CKSEL register, and bit 4 (WUTMMCK0) of the OSMC register.

WUTMMCK0 = 1: Oscillates

WUTMMCK0 = 0 and SELLOSC = 1: Oscillates

WUTMMCK0 = 0, SELLOSC = 0, and HPIEN = 1: Oscillates

WUTMMCK0 = 0, SELLOSC = 0, and HPIEN = 0: Stops

fWDT Set by bits 0 (WDSTBYON) and 4 (WDTON) of user option byte (000C0H/020C0H)

WDTON = 0: Stops

WDTON = 1 and WDSTBYON = 1: Oscillates

WDTON = 1 and WDSTBYON = 0: Stops

CPU Operation stopped

Code flash memory

Data flash memory

RAM Operation stopped (operation can continue during DTC transfer)

Port (latch) Status before HALT mode was set is retained

Timer array unit Operable (Operation is disabled while in the low consumption RTC mode)

Real-time clock (RTC) Operable

Watchdog timer See CHAPTER 11 WATCHDOG TIMER

Clock monitor Operation stopped

Timer RJ Operable (Operation is disabled while in the low consumption RTC mode)

Timer RD

Clock output/buzzer output

A/D converter Operation disabled

D/A converter

Comparator

Serial array unit (SAU) Operable (Operation is disabled while in the low consumption RTC mode)

Serial interface (IICA) Operation disabled

DTC Operable

ELC

Linking between operational function blocks is possible.

LIN/UART module (RLIN3) Operation disabled

CAN interface (RS-CAN lite)

Power-on-reset function Operable

Voltage detection function

External interrupt

Key interrupt function

Loading...

Loading...