RL78/F13, F14 CHAPTER 24 RESET FUNCTION

R01UH0368EJ0210 Rev.2.10 1549

Dec 10, 2015

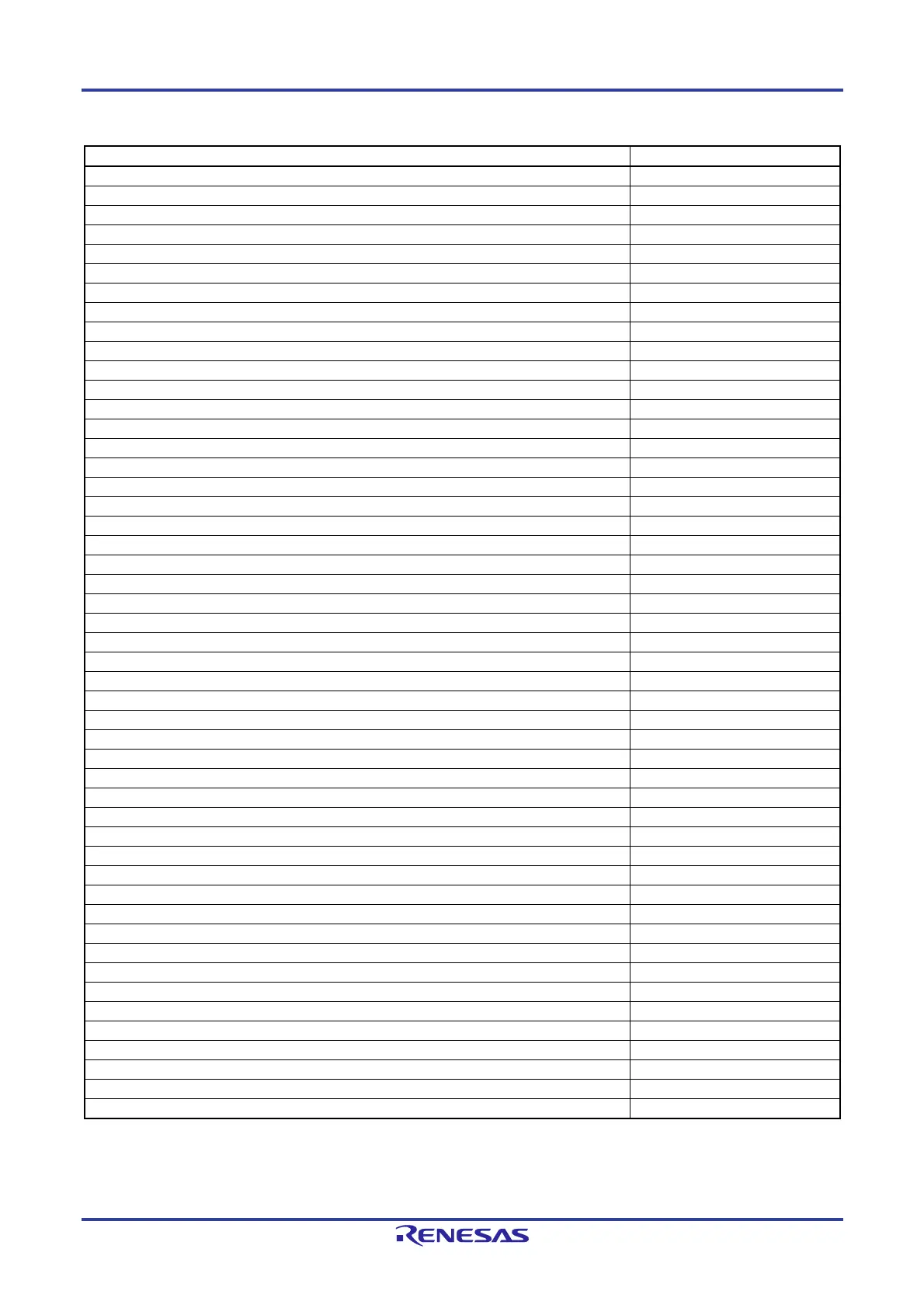

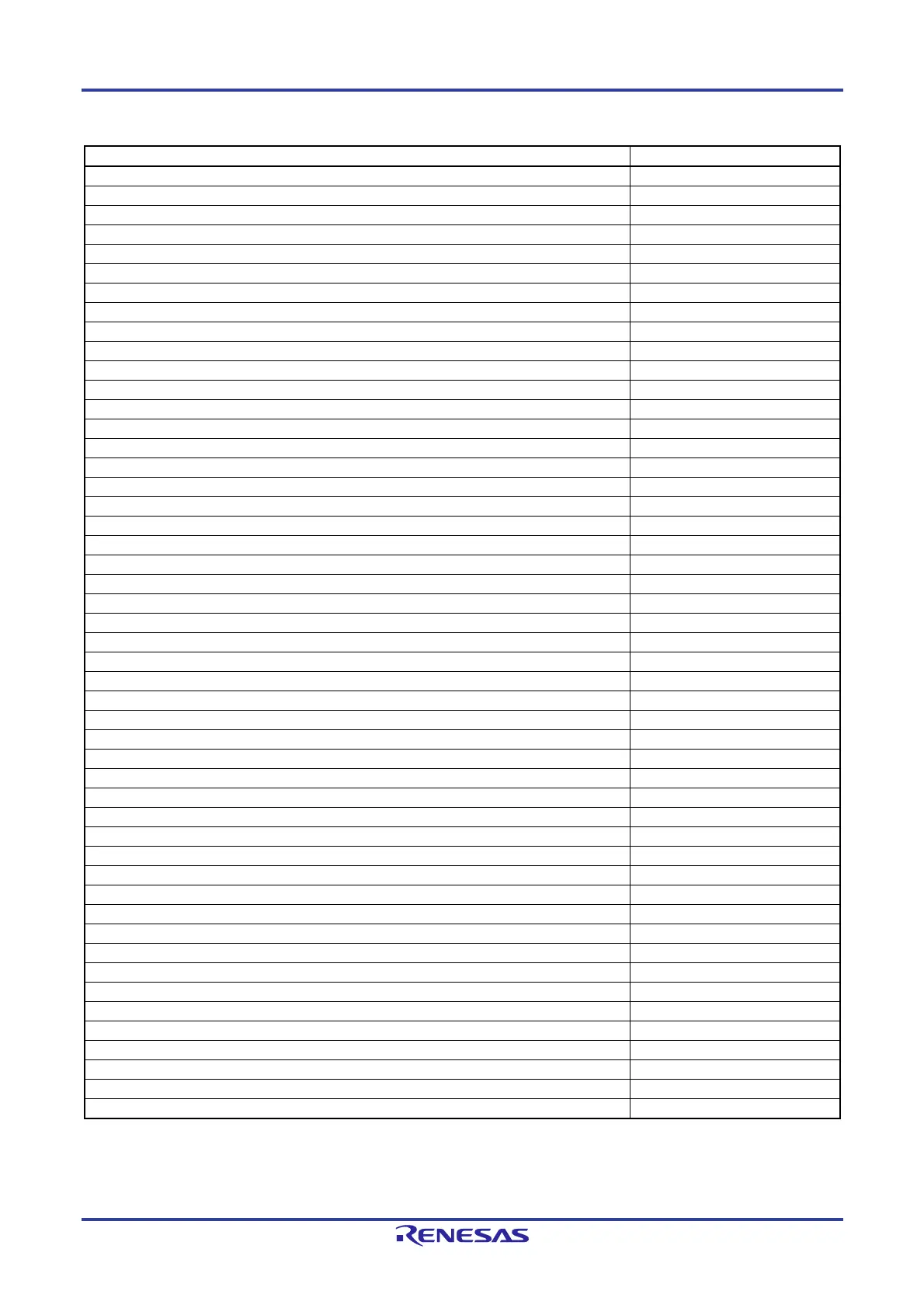

Table 24-2. States of Hardware After Acceptance of a Reset (3/4)

Hardware After Acceptance of a Reset

Note 1

Interrupt request flag register 3L (IF3L) 00H

Interrupt mask flag register 2 (MK2/L/H) FFH

Interrupt mask flag register 3 (MK3L) FFH

Priority specification flag register 02 (PR02/L/H) FFH

Priority specification flag register 03 (PR03L) FFH

Priority specification flag register 12 (PR12/L/H) FFH

Priority specification flag register 13 (PR13L) FFH

Interrupt request flag register 0 (IF0/L/H) 00H

Interrupt request flag register 1 (IF1/L/H) 00H

Interrupt mask flag register 0 (MK0/L/H) FFH

Interrupt mask flag register 1 (MK1/L/H) FFH

Priority specification flag register 00 (PR00/L/H) FFH

Priority specification flag register 01 (PR01/L/H) FFH

Priority specification flag register 10 (PR10/L/H) FFH

Priority specification flag register 11 (PR11/L/H) FFH

Multiply and accumulation register (L) (MACRL) 0000H

Multiply and accumulation register (H) (MACRH) 0000H

Processor mode control register (PMC) 00H

Comparator control register (CMPCTL) 00H

Comparator input and output switching register (CMPSEL) 00H

Comparator output monitor register (CMPMON) 00H

CAN clock select register (CANCKSEL) 00H

LIN clock select register (LINCKSEL) 00H

Clock select register (CKSEL) 00H

PLL control register (PLLCTL) 00H

PLL status register (PLLSTS) 00H

POR/CLM reset confirmation register (POCRES) Undefined

High-speed DTC control register 0 (HDTCCR0) 00H

High-speed DTC transfer count register 0 (HDTCCT0) 00H

High-speed DTC transfer count reload register 0 (HDTRLD0) 00H

High-speed DTC source address register 0 (HDTSAR0) 0000H

High-speed DTC destination address register 0 (HDTDAR0) 0000H

High-speed DTC control register 1 (HDTCCR1) 00H

High-speed DTC transfer count register 1 (HDTCCT1) 00H

High-speed DTC transfer count reload register 1 (HDTRLD1) 00H

High-speed DTC source address register 1 (HDTSAR1) 0000H

High-speed DTC destination address register 1 (HDTDAR1) 0000H

DTC base address register (DTCBAR) FDH

High-speed DTC channel select register 0 (SELHS0) 3FH

High-speed DTC channel select register 1 (SELHS1) 3FH

DTC activation enable register 0 (DTCEN0) 00H

DTC activation enable register 1 (DTCEN1) 00H

DTC activation enable register 2 (DTCEN2) 00H

DTC activation enable register 3 (DTCEN3) 00H

DTC activation enable register 4 (DTCEN4) 00H

DTC activation enable register 5 (DTCEN5)

Note 8

00H

CRC operation mode control register (CRCMD) 00H

CRC data register (CRCD) 0000H

LIN wakeup baud rate select register (LWBR0/LWBR1) 00H

(Notes and Remark are given below Table 24-2, States of Hardware After Acceptance of a Reset (4/4).)

Loading...

Loading...