RL78/F13, F14 CHAPTER 36 ELECTRICAL SPECIFICATIONS (GRADE Y)

R01UH0368EJ0210 Rev.2.10 1800

Dec 10, 2015

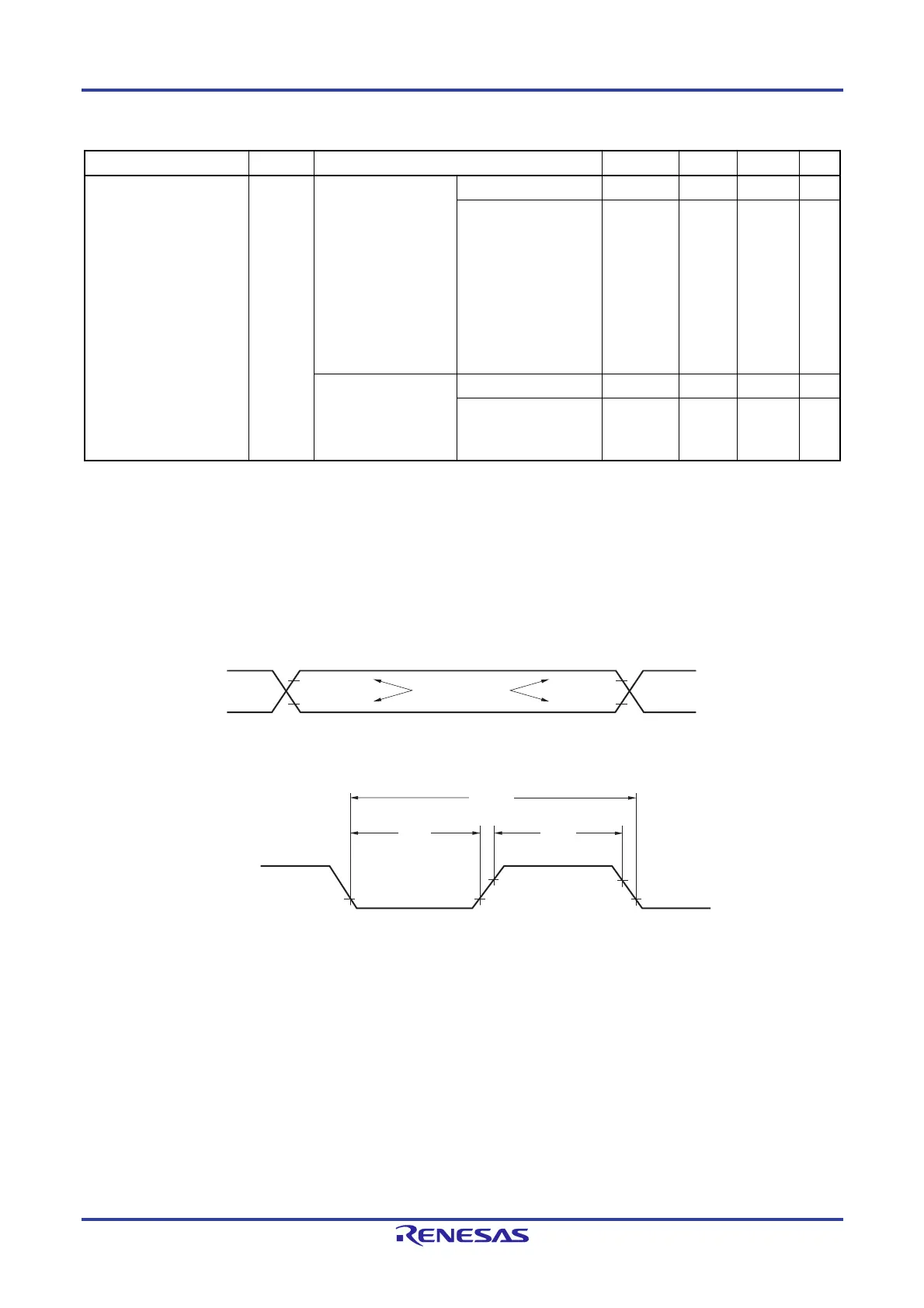

(TA = -40 to +150C, 2.7 V EVDD0 = EVDD1 = VDD 5.5 V, VSS = EVSS0 = EVSS1 = 0 V) (2/2)

Parameter Symbol Conditions MIN. TYP. MAX. Unit

Port output rise time, port

output fall time

t

RO, tFO

P00 to P03, P10 to

P17, P30 to P32, P40

to P47, P50 to P57,

P60 to P67, P70 to

P77, P96, P97, P106,

P107, P120, P125 to

P127, P130, P140,

P150 to 157

(normal slew rate)

C = 30 pF

4.0 V EV

DD0 5.5 V 25 ns

2.7 V EVDD0 < 4.0 V 55 ns

P10, P12, P14, P30,

P120, P140

(special slew rate)

C = 30 pF

4.0 V EV

DD0 5.5 V 25

Note

60 ns

2.7 V EVDD0 < 4.0 V 100 ns

Note TA = +25C, EVDD0 = 5.0 V

Caution Excluding the error in oscillation frequency accuracy.

Remark f

MCK: Timer array unit operation clock frequency

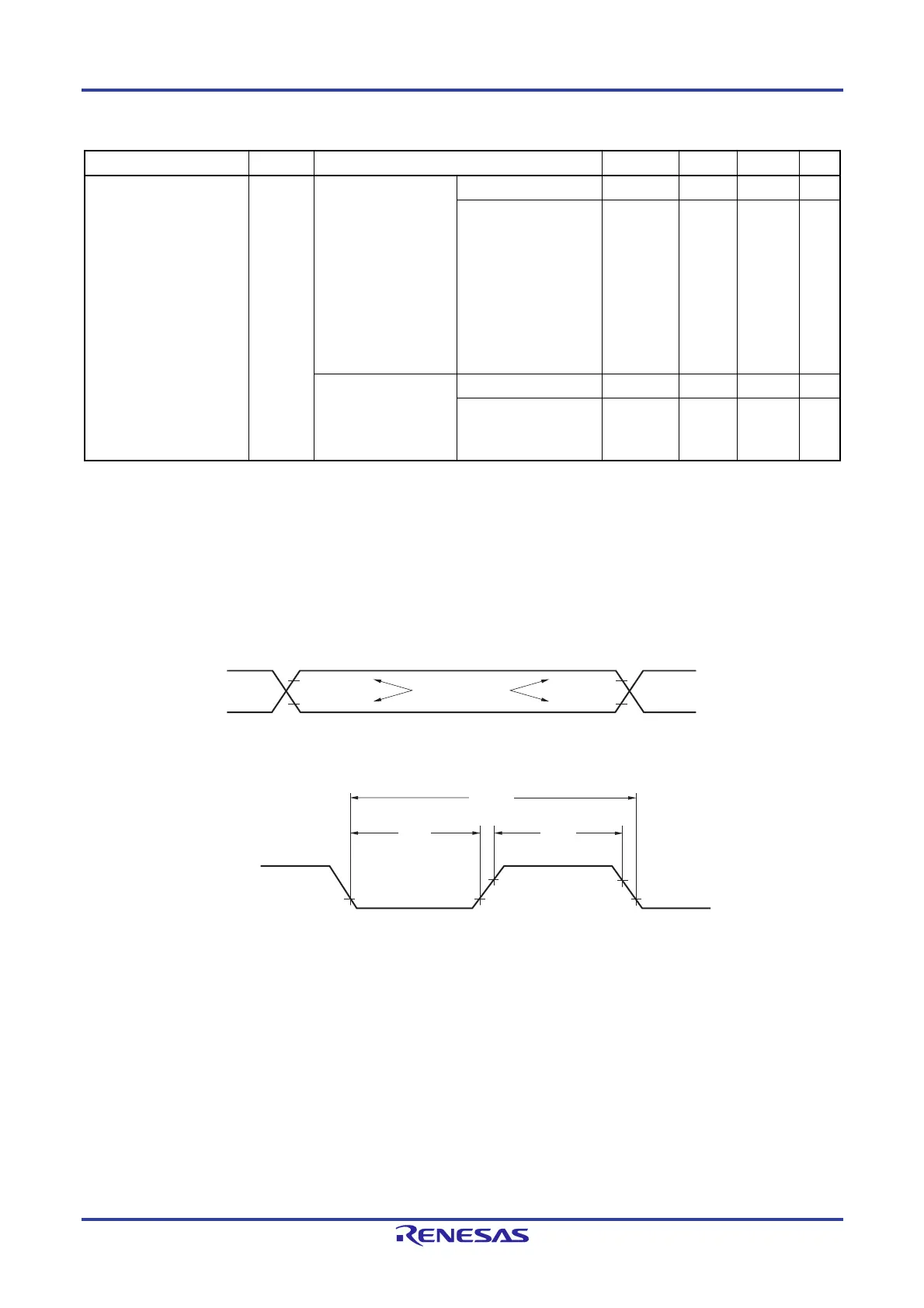

AC Timing Test Points

External System Clock Timing

VIH

VIL

Test points

V

IH

VIL

EXCLK

0.8 V

DD

(MIN.)

0.2 V

DD

(MAX.)

1/f

EX

t

EXL

t

EXH

Loading...

Loading...