RL78/F13, F14 CHAPTER 12 A/D CONVERTER

R01UH0368EJ0210 Rev.2.10 702

Dec 10, 2015

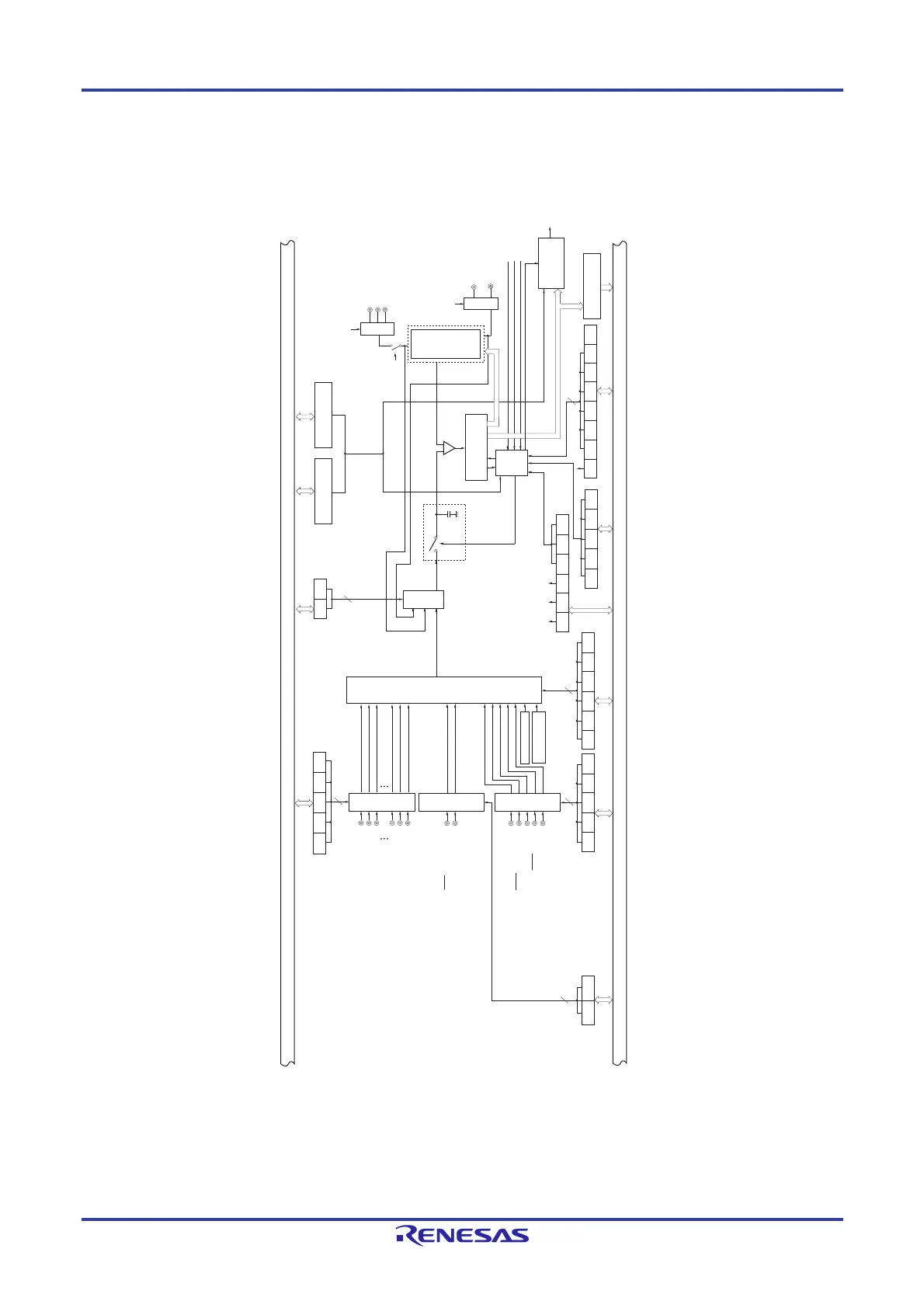

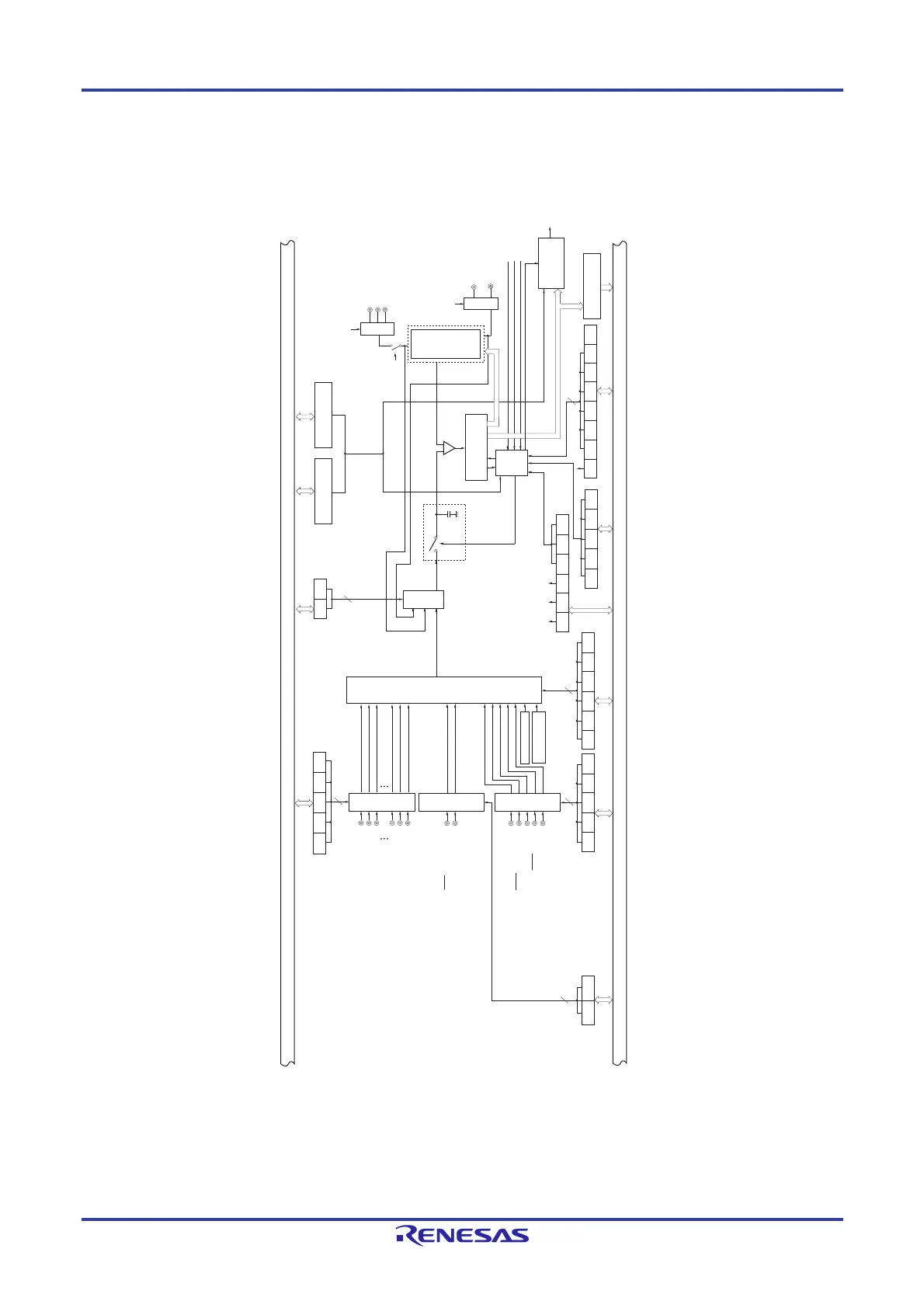

Figure 12-1. Block Diagram of A/D Converter

Notes 1. Only available in the RL78/F14.

2. Only available in the RL78/F13.

Remark Analog input pin for figure 12-1 when a 100-pin product of RL78/F14 is used.

INTAD

ADCS ADMD FR2 FR1 ADCEFR0

V

SS

6

2

5

ANI0/AV

REFP

/P33

ANI1/AV

REFM

/P34

ANI2/P80

ANI21/P103

ANI22/P104

ANI23/P105

Controller

INTRTC

LV1 LV0

6

ADPC4 ADPC2 ADPC1 ADPC0

ADTES1 ADTES0

5

2

ADS3ADS4 ADS2 ADS1 ADS0

ADISS

PMC73PMC74 PMC72 PMC71

PMC70

PMC120PMC125

ADREFPMADREFP0

ADRCK AWC ADTYP

ADREFP1

V

DD

P33/AV

REFP

/ANI0

P34/AV

REFM

/ANI1

V

SS

ADSCMADTMD0 ADTRS1 ADTRS0ADTMD1

ADREFM bit

INTTM01

ADPC3

Port mode control

register 12 (PMC12)

Port mode control

register 7 (PMC7)

ANI24/P125/TI03/TO03/TRDIOB0/SSI01/INTP1/SNZOUT1

ANI25/P120/TI07/T

O07/TRDIOD0/SO01/INTP4

ANI26/P70/KR0/TI15/TO15/INTP8/SI11/SDA11/SNZOUT4

ANI27/P71/KR1/TI17/TO17/INTP6/SCK11/SCL11/SNZOUT5

ANI28/P72/KR2/(CTXD0)/SO11/SNZOUT6

ANI29/P73/KR3/(CRXD0)/SSI11/SNZOUT7

ANI30/P74/KR4/(SO10)/(TXD1)

A/D port configuration

register (ADPC)

Analog/digital switcherAnalog/digital switcherAnalog/digital switcher

Selector

Selector

Selector

Selector

Internal bus

A/D test register

(ADTES)

Conversion result

comparison upper limit

setting register (ADUL)

Conversion result

comparison lower limit

setting register (ADLL)

Sample & hold circuit

A/D voltage comparator

Successive

approximation register

(SAR)

Comparison

voltage

generator

ADCS bit

ADREFP1 and ADREFP0 bits

Internal reference voltage (1.45 V)

Event signal

Note1

selected by ELC

or trigger signal

Note2

generated by

ADTRGS0 and ADTRGS1 registers

A/D conversion

result upper

limit/lower limit

comparator

A/D conversion result

register (ADCR)

A/D converter mode

register 0 (ADM0)

Internal bus

A/D converter mode

register 1 (ADM1)

A/D converter mode

register 2 (ADM2)

Analog input channel

specification register (ADS)

Temperature sensor

Internal reference

voltage (1.45 V)

Loading...

Loading...